FM24CL04 查看數據表(PDF) - Unspecified

零件编号

产品描述 (功能)

生产厂家

FM24CL04 Datasheet PDF : 12 Pages

| |||

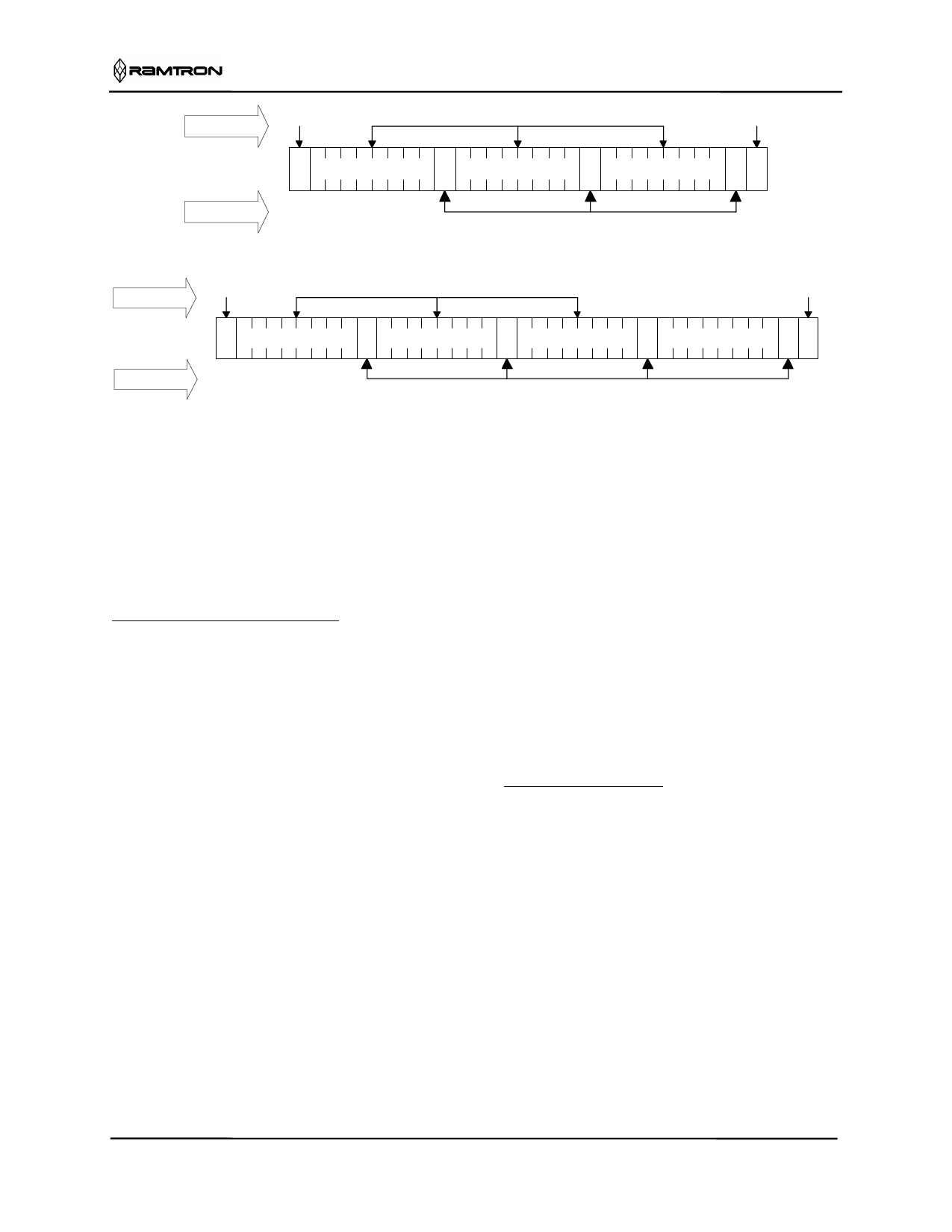

By Master

Start

Address & Data

FM24CL04

Stop

S Slave Address 0 A

Word Address

A

Data Byte

AP

By FM24CL04

Acknowledge

Figure 5. Byte Write

By Master

Start

Address & Data

S

Slave Address 0 A

Word Address

A

Data Byte

A

Data Byte

Stop

AP

By FM24CL04

Acknowledge

Figure 6. Multiple Byte Write

Read Operation

There are two basic types of read operations. They are

current address read and selective address read. In a

current address read, the FM24CL04 uses the internal

address latch to supply the lower 8 address bits. In a

selective read, the user performs a procedure to set

these lower address bits to a specific value.

Current Address & Sequential Read

The FM24CL04 uses an internal latch to supply the

lower 8 address bits for a read operation. A current

address read uses the existing value in the address

latch as a starting place for the read operation. This is

the address immediately following that of the last

operation.

To perform a current address read, the bus master

supplies a slave address with the LSB set to 1. This

indicates that a read operation is requested. The page

select bit in the slave address specifies the block of

memory that is used for the read operation. After the

acknowledge, the FM24CL04 will begin shifting out

data from the current address. The current address is

the bit from the slave address combined with the 8 bits

that were in the internal address latch.

Beginning with the current address, the bus master can

read any number of bytes. Thus a sequential read is

simply a current address read with multiple byte

transfers. After each byte the internal address counter

will be incremented. Each time the bus master

acknowledges a byte, this indicates that the

FM24CL04 should read out the next sequential byte.

There are four ways to properly terminate a read

operation. Failing to properly terminate the read will

most likely create a bus contention as the FM24CL04

attempts to read out additional data onto the bus. The

four valid methods are as follows.

1. The bus master issues a no-acknowledge in the

9th clock cycle and a stop in the 10th clock cycle.

This is illustrated in the diagrams below. This is

the preferred method.

2. The bus master issues a no-acknowledge in the

9th clock cycle and a start in the 10th.

3. The bus master issues a stop in the 9th clock

cycle. Bus contention may result.

4. The bus master issues a start in the 9th clock

cycle. Bus contention may result.

If the internal address reaches 1FFh it will wrap

around to 000h on the next read cycle. Figures 7 and

8 show the proper operation for current address reads.

Selective (Random) Read

A simple technique allows a user to select a random

address location as the starting point for a read

operation. This involves using the first two bytes of a

write operation to set the internal address byte

followed by subsequent read operations.

To perform a selective read, the bus master sends out

the slave address with the LSB set to 0. This specifies

a write operation. According to the write protocol, the

bus master then sends the word address byte that is

loaded into the internal address latch. After the

FM24CL04 acknowledges the word address, the bus

master issues a start condition. This simultaneously

aborts the write operation and allows the read

command to be issued with the slave address LSB set

to a 1. The operation is now a current address read.

See Figure 9.

Rev. 2.0

July 2003

Page 6 of 12