FM25C160 查看數據表(PDF) - Ramtron International Corporation

零件编号

产品描述 (功能)

生产厂家

FM25C160 Datasheet PDF : 13 Pages

| |||

Data Transfer

All data transfers to and from the FM25C160 occur

in 8-bit groups. They are synchronized to the clock

signal (SCK) and they transfer most significant bit

(MSB) first. Serial inputs are clocked in on the rising

edge of SCK. Outputs are driven on the falling edge

of SCK.

Command Structure

There are six commands called op-codes that can be

issued by the bus master to the FM25C160. They are

listed in the table below. These op-codes control the

functions performed by the memory. They can be

divided into three categories. First, are commands

that have no subsequent operations. They perform a

single function such as to enable a write operation.

Second are commands followed by one byte, either in

or out. They operate on the status register. Last are

commands for memory transactions followed by

address and one or more bytes of data.

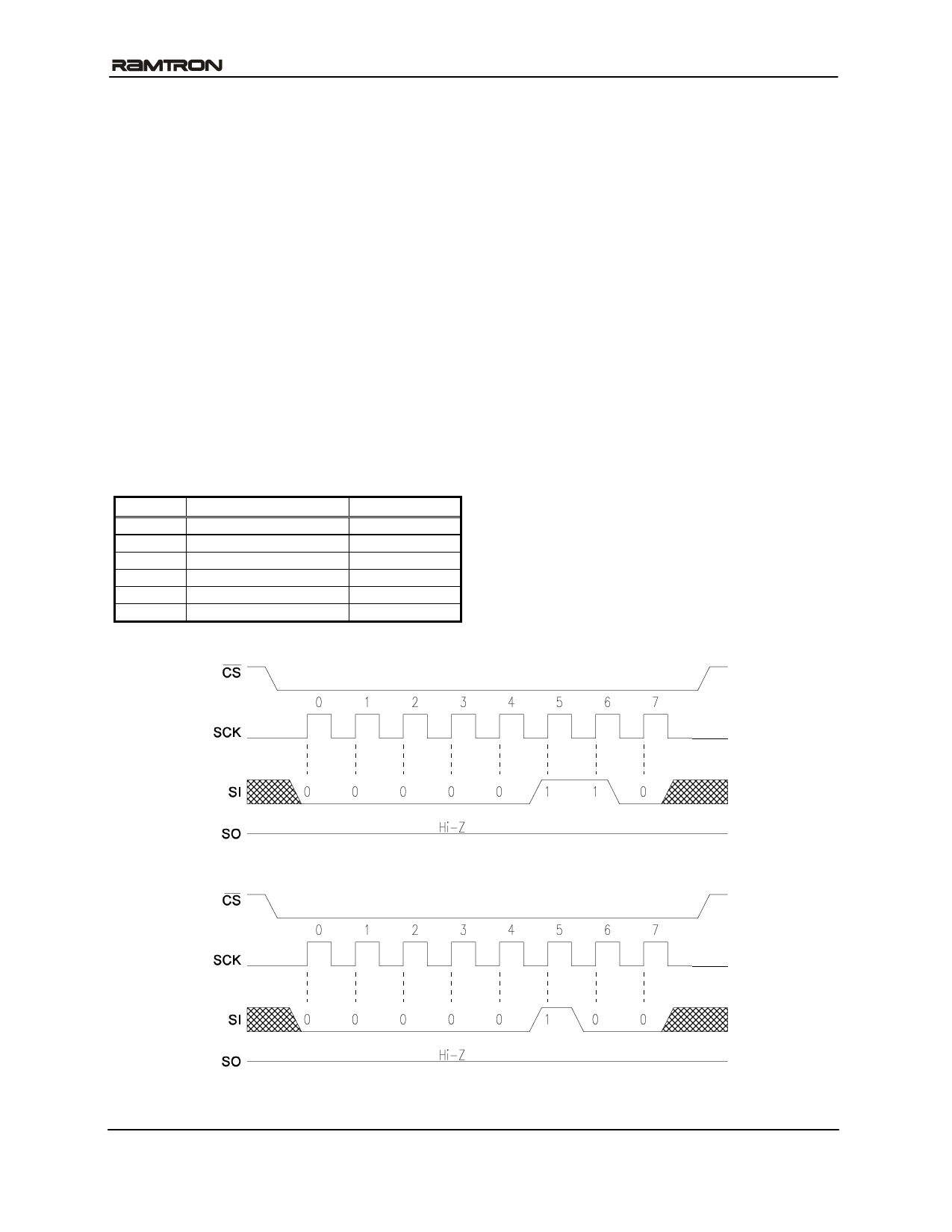

Table 1. Op-code Commands

Name Description

WREN Set Write Enable Latch

WRDI Write Disable

RDSR Read Status Register

WRSR Write Status Register

READ Read Memory Data

WRITE Write Memory Data

Op-code value

0000_0110b

0000_0100b

0000_0101b

0000_0001b

0000_0011b

0000_0010b

FM25C160 - Automotive Temp.

WREN - Set Write Enable Latch

The FM25C160 will power up with writes disabled.

The WREN command must be issued prior to any

write operation. Sending the WREN op-code will

allow the user to issue subsequent op-codes for write

operations. These include writing the status register

and writing the memory.

Sending the WREN op-code causes the internal Write

Enable Latch to be set. A flag bit in the status

register, called WEL, indicates the state of the latch.

WEL=1 indicates that writes are permitted. A write to

the status register has no effect on the WEL bit.

Completing any write operation will automatically

clear the write-enable latch and prevent further writes

without another WREN command. Figure 5 below

illustrates the WREN command bus configuration.

WRDI - Write Disable

The WRDI command disables all write activity by

clearing the Write Enable Latch. The user can verify

that writes are disabled by reading the WEL bit in the

status register and verifying that WEL=0. Figure 6

illustrates the WRDI command bus configuration.

Figure 5. WREN Bus Configuration

Rev. 3.1

July 2007

Figure 6. WRDI Bus Configuration

Page 5 of 13