HEC4027BT 查看數據表(PDF) - Philips Electronics

零件编号

产品描述 (功能)

生产厂家

HEC4027BT Datasheet PDF : 5 Pages

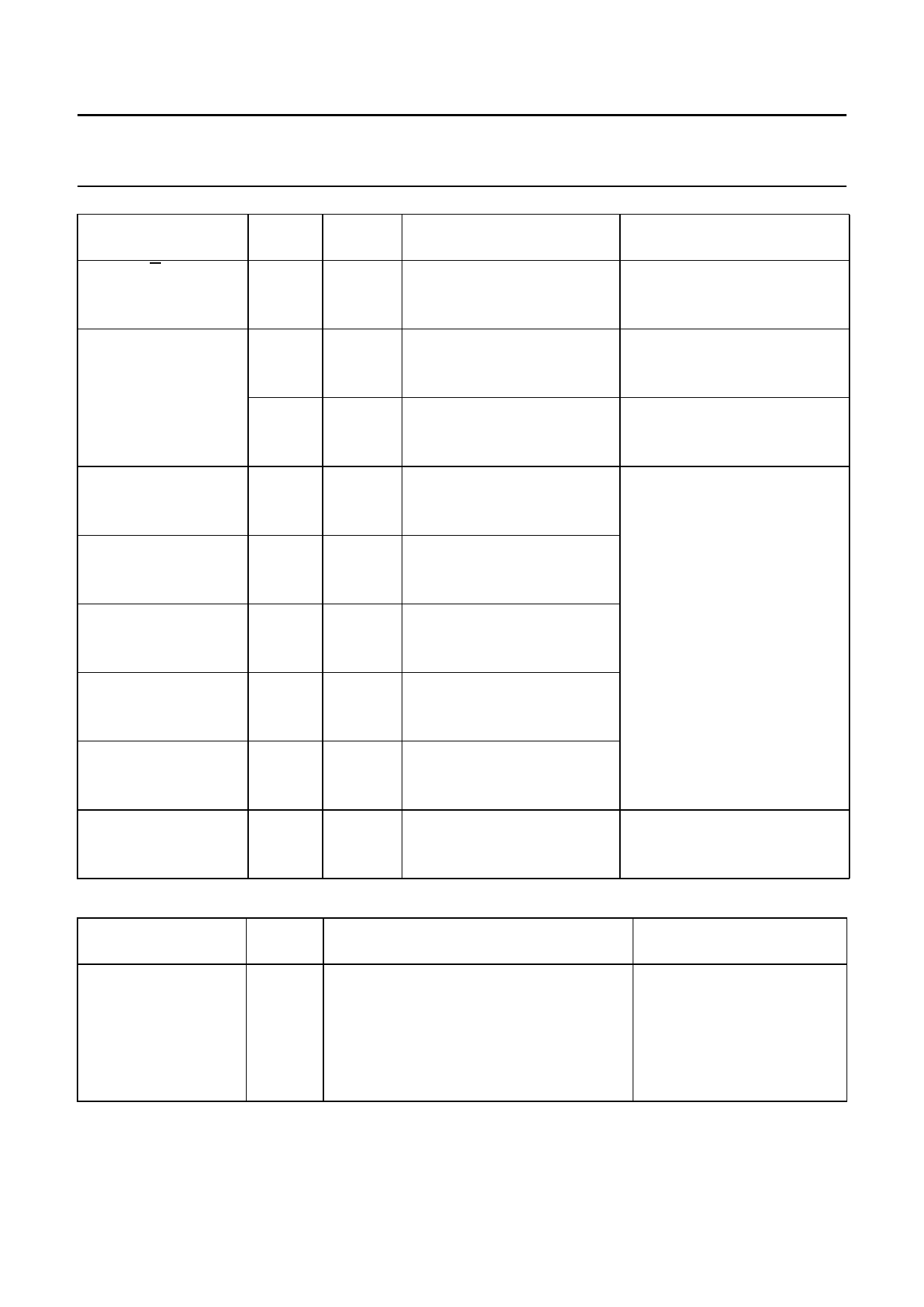

| |||

Philips Semiconductors

Dual JK flip-flop

Product specification

HEF4027B

flip-flops

CD → O

LOW to HIGH

Output transition times

HIGH to LOW

LOW to HIGH

Set-up time

J,K → CP

Hold time

J,K → CP

Minimum clock

pulse width; LOW

Minimum SD, CD

pulse width; HIGH

Recovery time

for SD, CD

Maximum clock

pulse frequency

J = K = HIGH

VDD

V

SYMBOL MIN. TYP. MAX.

TYPICAL EXTRAPOLATION

FORMULA

5

10 tPLH

15

5

10 tTHL

15

5

10 tTLH

15

5

75

150 ns

35

70 ns

25

50 ns

60

120 ns

30

60 ns

20

40 ns

60

120 ns

30

60 ns

20

40 ns

50

25

ns

48 ns + (0,55 ns/pF) CL

24 ns + (0,23 ns/pF) CL

17 ns + (0,16 ns/pF) CL

10 ns + (1,0 ns/pF) CL

9 ns + (0,42 ns/pF) CL

6 ns + (0,28 ns/pF) CL

10 ns + (1,0 ns/pF) CL

9 ns + (0,42 ns/pF) CL

6 ns + (0,28 ns/pF) CL

10 tsu

30

10

ns

15

20

5

ns

5

25

0

ns

10 thold

20

0

ns

15

15

5

ns

5

10 tWCPL

15

80

40

30

15

24

12

ns

ns

see also waveforms

Figs 4 and 5

ns

5

90

45

ns

10

tWSDH,

tWCDH

40

20

ns

15

30

15

ns

5

20

−15

ns

10

tRSD,

tRCD

15

−10

ns

15

10

−5

ns

5

10 fmax

15

4

8

12

25

15

30

MHz

MHz

MHz

see also waveforms

Fig.4

VDD

V

TYPICAL FORMULA FOR P (µW)

Dynamic power

5

dissipation per

10

package (P)

15

900 fi + ∑ (foCL) × VDD2

4 500 fi + ∑ (foCL) × VDD2

13 200 fi + ∑ (foCL) × VDD2

where

fi = input freq. (MHz)

fo = output freq. (MHz)

CL = load capacitance (pF)

∑ (foCL) = sum of outputs

VDD = supply voltage (V)

January 1995

4