HV9982 查看數據表(PDF) - Supertex Inc

零件编号

产品描述 (功能)

生产厂家

HV9982 Datasheet PDF : 13 Pages

| |||

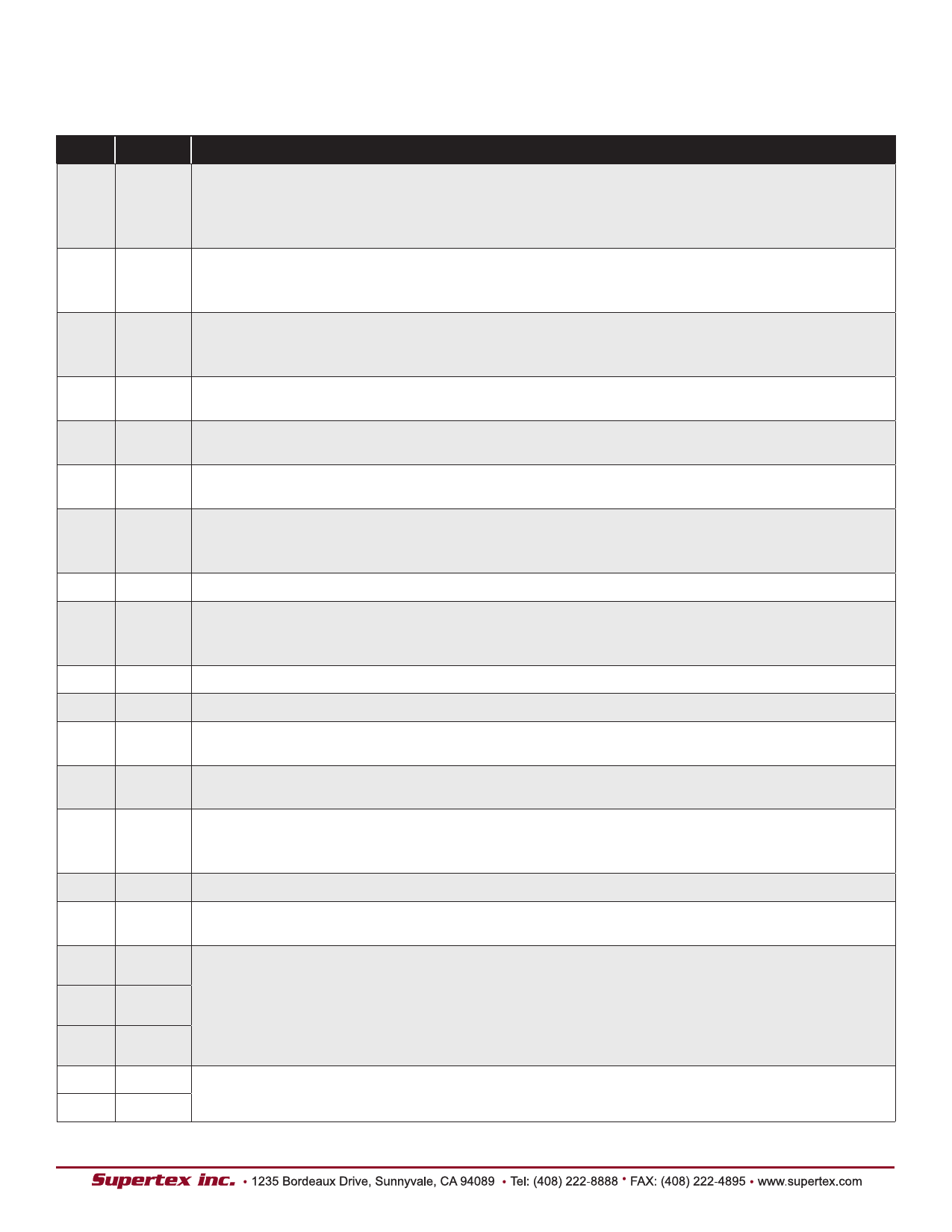

HV9982

Pin Description

Pin #

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

Name Description

VDD1

FLT1

CS1

COMP1

FDBK1

REF1

OVP1

Power supply pin for channel 1. It can either be connected to the VDD pin or supplied with an external

power supply. It must be bypassed with a low ESR capacitor to GND1 (at least 0.1μF). All VDD pins

(VDD, VDD1-3) must be connected together externally. An external supply (7V – 9V) can be con-

nected to these pins to power the IC if the internal regulator is not used.

Used to drive an external disconnect switch. The disconnect switch is used to protect the LEDs in case

of fault conditions and also help to provide excellent PWM dimming response by disconnecting and

reconnecting the LEDs from the output capacitor during PWM dimming.

Used to sense the source current of the external power FET used with channel 1. It includes a built-in

100ns (min) blanking timer. An R-C network at this pin programs the slope compensation. Refer to the

Slope Compensation section for additional information.

Stable closed loop control for channel 1 can be accomplished by connecting a compensation network

between each COMP1 pin and GND1.

Output current feedback input for channel 1. It receives a voltage signal from an external sense resis-

tor.

The voltage at this pin sets the output current level for channel 1. Recommended voltage range for

this pin is 0V – 1.25V.

Provides the over voltage protection for the channel 1. When the voltage at this pin exceeds 5.0V, the

HV9982 is turned off and the fault timer starts. Upon completion of the fault timer the IC attempts to

restart.

VIN Input of the internal 40V linear regulator.

VDD

Output of the linear regulator. It maintains a regulated 7.75V as long as the voltage of the VIN pin is

between 10V and 40V. It must be bypassed with a low ESR capacitor to GND (at least 0.1μF). Can be

used as a power supply for the three channels.

EN When pin is pulled below 0.8V, the IC goes into a standby mode and draws minimal current.

GND Ground connection for the common circuitry in the HV9982.

COMP2

REF2

OVP2

Stable closed loop control for channel 2 can be accomplished by connecting a compensation network

between each COMP2 pin and GND2.

The voltage at this pin sets the output current level for channel 2. Recommended voltage range for

this pin is 0V – 1.25V.

Provides the over voltage protection for the channel 2. When the voltage at this pin exceeds 5.0V, the

HV9982 is turned off and the fault timer starts. Upon completion of the fault timer the IC attempts to

restart.

SKIP Programs the hiccup timer for fault conditions. A capacitor to GND programs the hiccup time.

RAMP

Provides a ramp signal which is used while dimming the channels with pulse-width modulation with an

analog input. A capacitor to GND programs the PWM dimming frequency.

17 PWMD1 PWM dimming of the three channels is accomplished by using the PWMD pins. If S1 is LOW, then the

18

PWMD2

three pins directly control the PWM dimming of the three channels and a square wave input should be

applied at these pins. If S1 is high, then a 0V – 2.0V analog signal should be applied at these pins. The

19 PWMD3 PWM dimming is then done by comparing the analog voltage to the voltage at the RAMP pin.

20

S1 Digital input pins which select the operating mode of the PWMD inputs. Refer to the PWM dimming

21

S2 section for additional information.

11