ICS853001 查看數據表(PDF) - Integrated Circuit Systems

零件编号

产品描述 (功能)

生产厂家

ICS853001 Datasheet PDF : 16 Pages

| |||

Integrated

Circuit

Systems, Inc.

ICS853001

1:1, DIFFERENTIAL LVPECL-TO-

2.5V, 3.3V, 5V LVPECL/ECL BUFFER

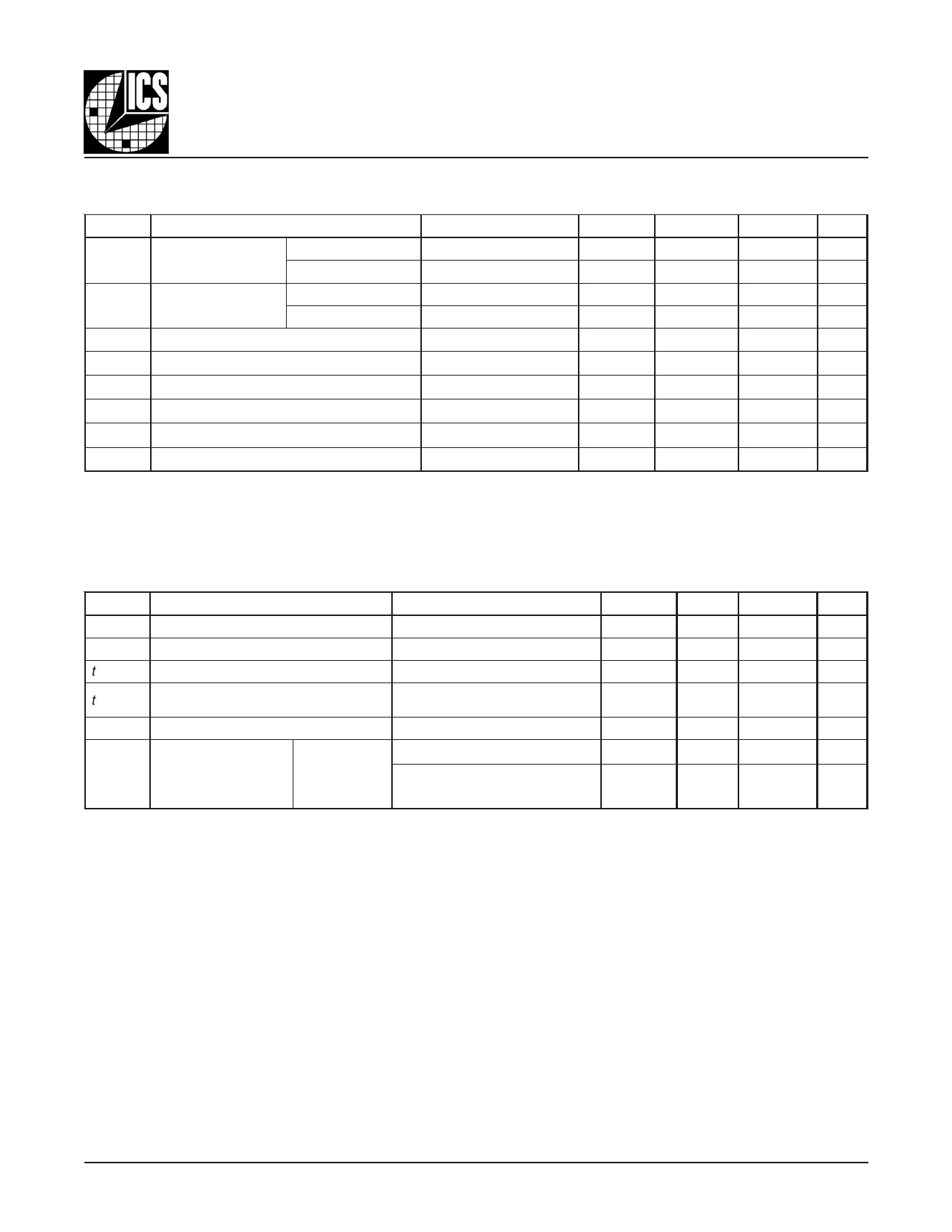

TABLE 3D. LVPECL DC CHARACTERISTICS, VCC = 2.375V TO 5.25V; VEE = 0V, TA = -40°C TO 85°C

Symbol Parameter

Test Conditions Minimum Typical

PCLK

IIH

Input High Current

nPCLK

VCC = VIN

VCC = VIN

PCLK

IIL

Input Low Current

nPCLK

VCC = 5.25, VIN = 0V

VCC = 5.25V, VIN = 0V

-200

-200

VPP

Peak-to-Peak Input Voltage

0.15

VCMR

Common Mode Input Voltage; NOTE 1, 2

1.2

VOH

Output High Voltage; NOTE 3

VCC - 1.005

VOL

Output Low Voltage; NOTE 3

VCC - 1.78

VSWING Peak-to-Peak Output Voltage Swing

0.6

VBB

Bias Voltage

VCC - 1.44 VCC - 1.38

NOTE 1: Common mode voltage is defined as VIH.

NOTE 2: For single ended applications, the maximum input voltage for PCLK, nPCLK is VCC + 0.3V.

NOTE 3: Outputs terminated with 50Ω to VCC - 2V.

Maximum

200

200

1.2

VCC

1.0

VCC - 1.32

Units

µA

µA

µA

µA

V

V

V

V

V

V

TABLE

4.

AC

CHARACTERISTICS,

V

CC

=

0V;

V

EE

=

-5.25V

TO

-2.375V

OR

V

CC

=

2.375

TO

5.25V;

V

EE

=

0V,

TA

=

-40°C

TO

85°C

Symbol Parameter

Test Conditions

Minimum Typical Maximum Units

fMAX

Output Frequency

tPD

Propagation Delay; NOTE 1

250

tsk(pp) Part-to-Part Skew; NOTE 2, 3

tjit

Buffer Additive Phase Jitter, RMS; 155.52MHz, Integration Range:

refer to Additive Phase Jitter Section

12KHz - 20MHz

0.03

t /t

RF

Output Rise/Fall Time

20% to 80%

50

VCC = 2.375V to 3.6V, VEE = 0

48

odc

Output Duty Cycle

IJ 1GHz VCC > 3.6V to 5.25V, VEE = 0 or

46

VEE = -5.25V to -3.6V,VCC = 0

All parameters are measured at IJ 1.7GHz, unless otherwise noted.

NOTE 1: Measured from the differential input crossing point to the differential output crossing point.

NOTE 2: Defined as skew between outputs on different devices operating at the same supply voltages and

with equal load conditions. Using the same type of inputs on each device, the outputs are measured

at the differential cross points.

NOTE 3: This parameter is defined in accordance with JEDEC Standard 65.

>2.5

500

100

250

52

54

GHz

ps

ps

ps

ps

%

%

853001AG

www.icst.com/products/hiperclocks.html

4

REV. A JANUARY 29, 2005