IDT7201LA80P(1997) 查看數據表(PDF) - Integrated Device Technology

零件编号

产品描述 (功能)

生产厂家

IDT7201LA80P

(Rev.:1997)

(Rev.:1997)

IDT7201LA80P Datasheet PDF : 13 Pages

| |||

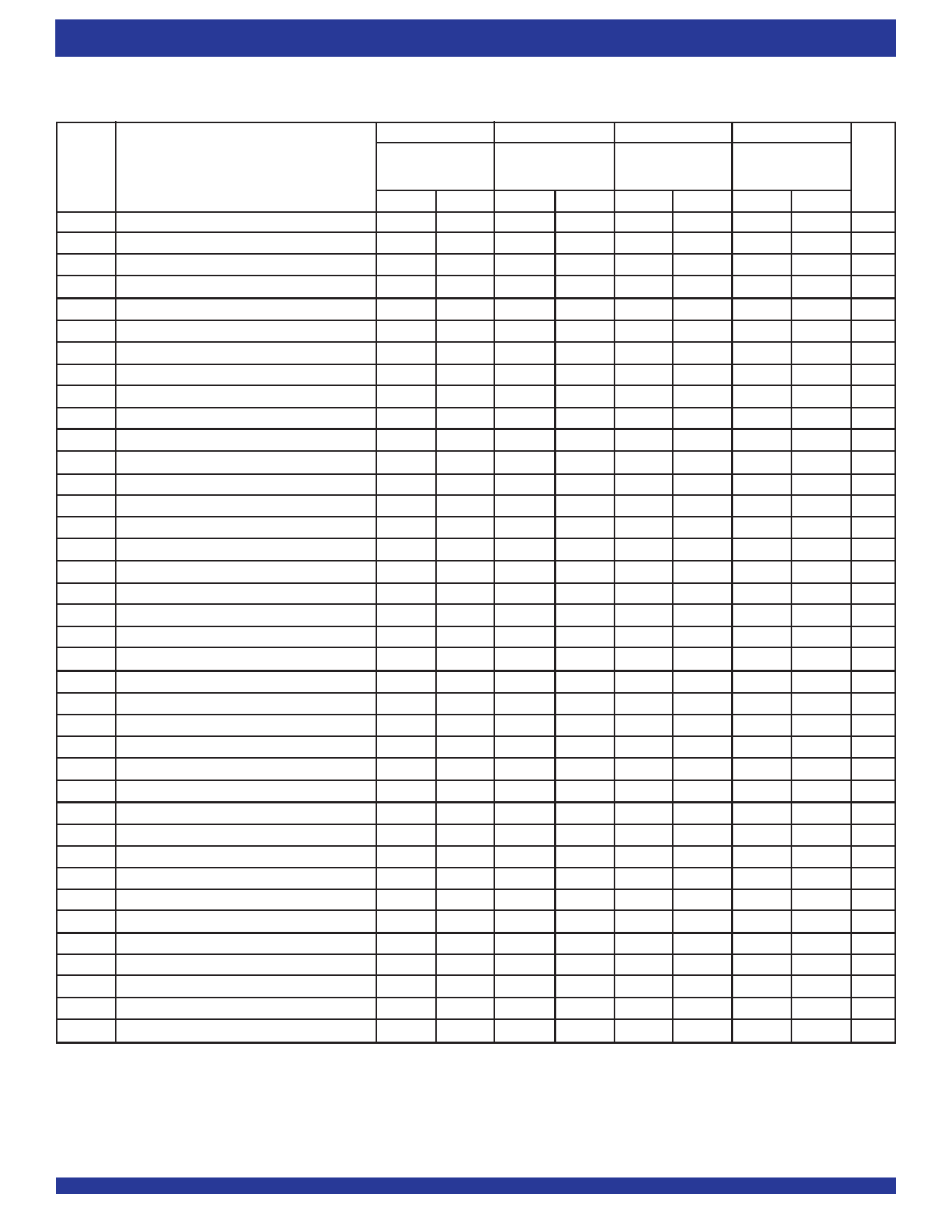

IDT7200/7201A/7202A CMOS ASYNCHRONOUS FIFO

256 x 9, 512 x 9 and 1,024 x 9

MILITARY, INDUSTRIAL AND COMMERCIAL TEMPERATURE RANGES

AC ELECTRICAL CHARACTERISTICS(1) (Continued)

(Commercial: VCC = 5V ± 10%, TA = 0°C to +70°C; Industrial: VCC = 5V ± 10%, TA = –40°C to +85°C; Military: VCC = 5V ± 10%, TA = –55°C to +125°C)

Military Com'l & Mil.

Military(2)

7200 L40

7201LA40

7202LA40

7200L50

7201LA50

7202LA50

7200L65

7201LA65

7202LA65

7200L80

7201LA80

7202LA80

7200L120

7201LA120

7202LA120

Symbol

Parameter

Min. Max. Min. Max. Min. Max. Min. Max. Min. Max. Unit

tS

Shift Frequency

—

20 — 15 — 12.5 — 10 —

7 MHz

tRC

Read Cycle Time

50

— 65 — 80 — 100 — 140 — ns

tA

Access Time

—

40 — 50 — 65 — 80 — 120 ns

tRR

tRPW

tRLZ

tWLZ

Read Recovery Time

10

Read Pulse Width(3)

40

Read Pulse Low to Data Bus at Low Z(4) 5

Write Pulse High to Data Bus at Low Z(4, 5) 10

— 15 — 15 — 20 — 20 — ns

— 50 — 65 — 80 — 120 — ns

— 10 — 10 — 10 — 10 — ns

— 15 — 15 — 20 — 20 — ns

tDV

Data Valid from Read Pulse High

5

tRHZ

Read Pulse High to Data Bus at High Z(4) —

—5 —

5—5—

5

— ns

25 — 30 — 30 — 30 — 35 ns

tWC

tWPW

Write Cycle Time

Write Pulse Width(3)

50

— 65 — 80 — 100 — 140 — ns

40

— 50 — 65 — 80 — 120 — ns

tWR

Write Recovery Time

10

— 15 — 15 — 20 — 20 — ns

tDS

Data Set-up Time

20

— 30

—

30 — 40 —

40

—

ns

tDH

Data Hold Time

0

—5

— 10 — 10 — 10 — ns

tRSC

tRS

tRSS

Reset Cycle Time

Reset Pulse Width(3)

Reset Set-up Time(4)

50

— 65

—

80 — 100 — 140 —

ns

40

— 50

—

65 — 80 — 120 —

ns

40

— 50

—

65 — 80 — 120 —

ns

tRSR Reset Recovery Time

10

— 15

—

15 — 20 —

20

—

ns

tRTC Retransmit Cycle Time

tRT

Retransmit Pulse Width(3)

tRTS

Retransmit Set-up Time(4)

50

— 65

—

80 — 100 — 140 —

ns

40

— 50 — 65 — 80 — 120 — ns

40

— 50 — 65 — 80 — 120 — ns

tRTR Retransmit Recovery Time

10

— 15 — 15 — 20 — 20 — ns

tEFL

Reset to Empty Flag Low

—

50 — 65 — 80 — 100 — 140 ns

tHFH,FFH Reset to Half-Full and Full Flag High

—

50 — 65 — 80 — 100 — 140 ns

tRTF Retransmit Low to Flags Valid

—

50 — 65 — 80 — 100 — 140 ns

tREF Read Low to Empty Flag Low

—

30 — 45 — 60 — 60 — 60 ns

tRFF Read High to Full Flag High

tRPE

Read Pulse Width after EF High

—

35 — 45 — 60 — 60 — 60 ns

40

— 50 — 65 — 80 — 120 — ns

tWEF Write High to Empty Flag High

—

35 — 45 — 60 — 60 — 60 ns

tWFF Write Low to Full Flag Low

—

35 — 45 — 60 — 60 — 60 ns

tWHF Write Low to Half-Full Flag Low

—

50 — 65 — 80 — 100 — 140 ns

tRHF

tWPF

tXOL

tXOH

tXI

tXIR

tXIS

Read High to Half-Full Flag High

Write Pulse Width after FF High

Read/Write to XO Low

Read/Write to XO High

XI Pulse Width(3)

XI Recovery Time

XI Set-up Time

—

50 — 65 — 80 — 100 — 140 ns

40

— 50 — 65 — 80 — 120 — ns

—

40 — 50 — 65 — 80 — 120 ns

—

40 — 50 — 65 — 80 — 120 ns

40

— 50 — 65 — 80 — 120 — ns

10

— 10 — 10 — 10 — 10 — ns

10

— 15 — 15 — 15 — 15 — ns

NOTES:

1. Timings referenced as in AC Test Conditions

2. Speed grades 65, 80 and 120 not available in the CERPACK

3. Pulse widths less than minimum value are not allowed.

4. Values guaranteed by design, not currently tested.

5. Only applies to read data flow-through mode.

2679 tbl 07

5