LT1371 查看數據表(PDF) - Linear Technology

零件编号

产品描述 (功能)

生产厂家

LT1371 Datasheet PDF : 16 Pages

| |||

UU W U

APPLICATIO S I FOR ATIO

maximum output load current and will also be increased if

poor quality (high ESR) output capacitors are used. The

addition of a 0.0047µF capacitor on the VC pin reduces

switching frequency ripple to only a few millivolts. A low

value for RC will also reduce VC pin ripple, but loop phase

margin may be inadequate.

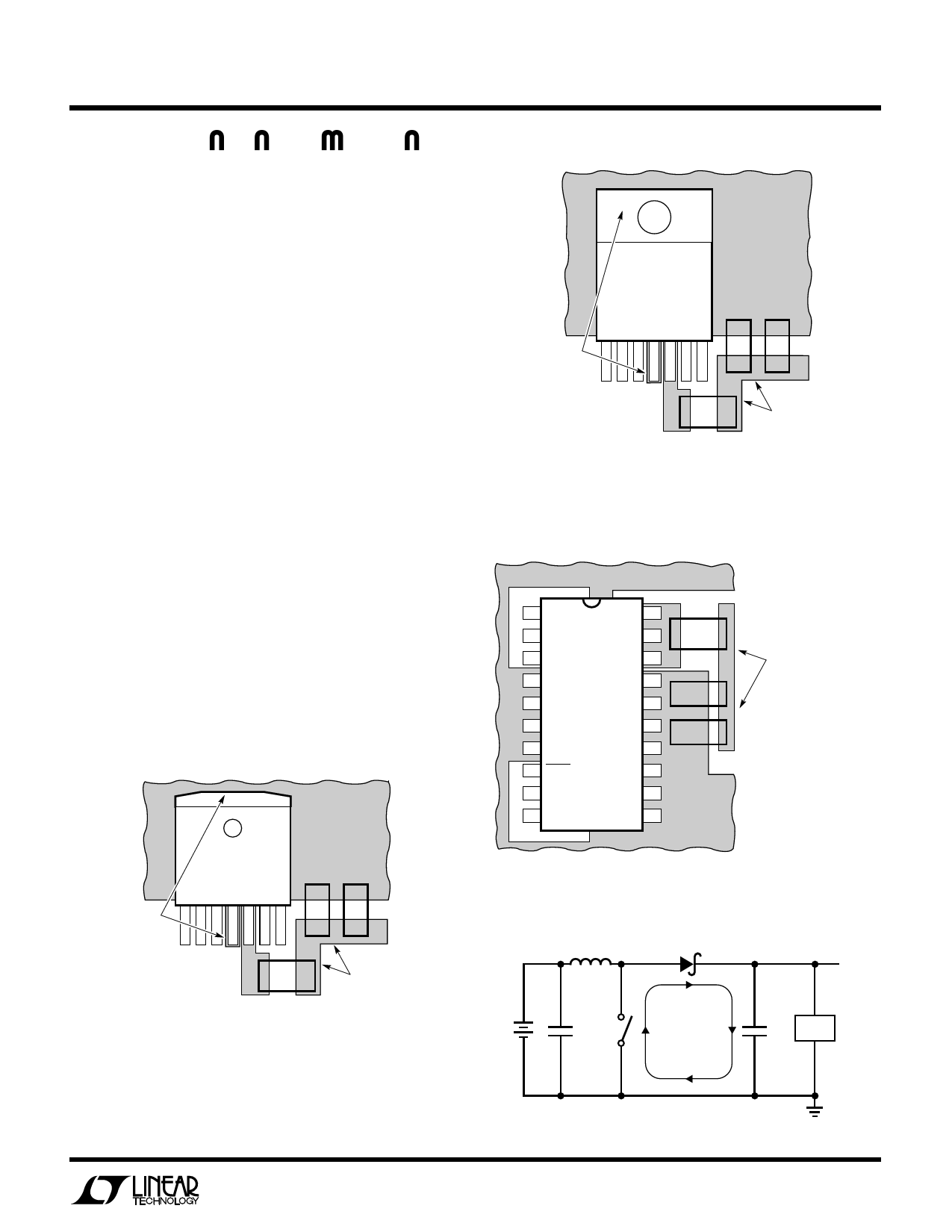

Layout Considerations

For maximum efficiency, LT1371 switch rise and fall times

are made as short as possible. To prevent radiation and

high frequency resonance problems, proper layout of the

components connected to the switch node is essential. B

field (magnetic) radiation is minimized by keeping output

diode, Switch pin and output bypass capacitor leads as

short as possible. Figures 3, 4 and 5 show recommended

positions for these components. E field radiation is kept

low by minimizing the length and area of all traces con-

nected to the Switch pin. A ground plane should always be

used under the switcher circuitry to prevent interplane

coupling.

The high speed switching current path is shown schemati-

cally in Figure 6. Minimum lead length in this path is

essential to ensure clean switching and low EMI. The path

including the switch, output diode and output capacitor is

the only one containing nanosecond rise and fall times.

Keep this path as short as possible.

LT1371

FB GND S/S

VC NFB VSW VIN

CONNECT

GROUND PIN

AND TAB DIRECTLY

TO GROUND PLANE.

TAB MAY BE

SOLDERED OR

BOLTED TO

GROUND PLANE*

C

D

C

KEEP PATH FROM

VSW, OUTPUT DIODE,

OUTPUT CAPACITORS

AND GROUND RETURN

AS SHORT AS POSSIBLE

*SEE T7 PACKAGE LAYOUT CONSIDERATIONS FOR VERTICAL MOUNTING

OF THE T7 PACKAGE

LT1371 • F04

Figure 4. Layout Considerations— T7 Package

VC

VSW

FB

NC

D

NFB

VSW

GND

GND

C

GND

GND

GND

GND

C

GND

GND

SHDN

NC

SYNC

NC

VIN

GND

KEEP PATH FROM

VSW, OUTPUT DIODE,

OUTPUT CAPACITORS

AND GROUND RETURN

AS SHORT AS POSSIBLE

FB GND S/S

VC NFB VSW VIN

CONNECT

C

GROUND PIN

AND TAB DIRECTLY

TO GROUND PLANE

D

C

KEEP PATH FROM

VSW, OUTPUT DIODE,

OUTPUT CAPACITORS

AND GROUND RETURN

AS SHORT AS POSSIBLE

LT1371 • F03

Figure 3. Layout Considerations— R Package

CONNECT ALL GROUND PINS TO GROUND PLANE

LT1371 • F05

Figure 5. Layout Considerations— SW Package

SWITCH

L1 NODE

VOUT

HIGH

VIN

FREQUENCY

LOAD

CIRCULATING

PATH

Figure 6

LT1371 • F06

11