M48Z129V-85PM1(2000) жҹҘзңӢж•ёж“ҡиЎЁпјҲPDFпјү - STMicroelectronics

йӣ¶д»¶зј–еҸ·

дә§е“ҒжҸҸиҝ° (еҠҹиғҪ)

з”ҹдә§еҺӮ家

M48Z129V-85PM1 Datasheet PDF : 13 Pages

| |||

M48Z129Y, M48Z129V

Table 4. AC Measurement Conditions

Input Rise and Fall Times

вүӨ 5ns

Input Pulse Voltages

0 to 3V

Input and Output Timing Ref. Voltages

1.5V

Note that Output Hi-Z is defined as the point where data is no longer

driven.

Note: A power failure during a write cycle may

corrupt data at the current addressed location, but

does not jeopardize the rest of the RAMвҖҷs content.

At voltages below VPFD(min), the memory will be

in a write protected state, provided the VCC fall

time is not less than tF. The M48Z129Y/V may re-

spond to transient noise spikes on VCC that cross

into the deselect window during the time the de-

vice is sampling VCC. Therefore, decoupling of the

power supply lines is recommended.

When VCC drops below VSO, the control circuit

switches power to the internal battery, preserving

data. The internal energy source will maintain

data in the M48Z129Y/V for an accumulated peri-

od of at least 10 years at room temperature. As

system power rises above VSO, the battery is dis-

connected, and the power supply is switched to

external VCC. Deselect continues for tREC after

VCC reaches VPFD(max).

For more information on Battery Storage Life refer

to the Application Note AN1012.

POWER-ON RESET OUTPUT

All microprocessors have a reset input which forc-

es them to a known state when starting. The

M48Z129Y/V has a reset output (RST) pin which

is guaranteed to be low below VPFD(min). This sig-

nal is an open drain configuration. An appropriate

pull-up resistor should be chosen to control the

rise time. This signal will be valid for all voltage

conditions, even when VCC equals VSS. Once VCC

exceeds the power failure detect voltage VPFD, an

internal timer keeps RST low for tREC to allow the

power supply to stabilize.

BATTERY LOW PIN

The M48Z129Y/V automatically performs battery

voltage monitoring upon power-up, and at factory-

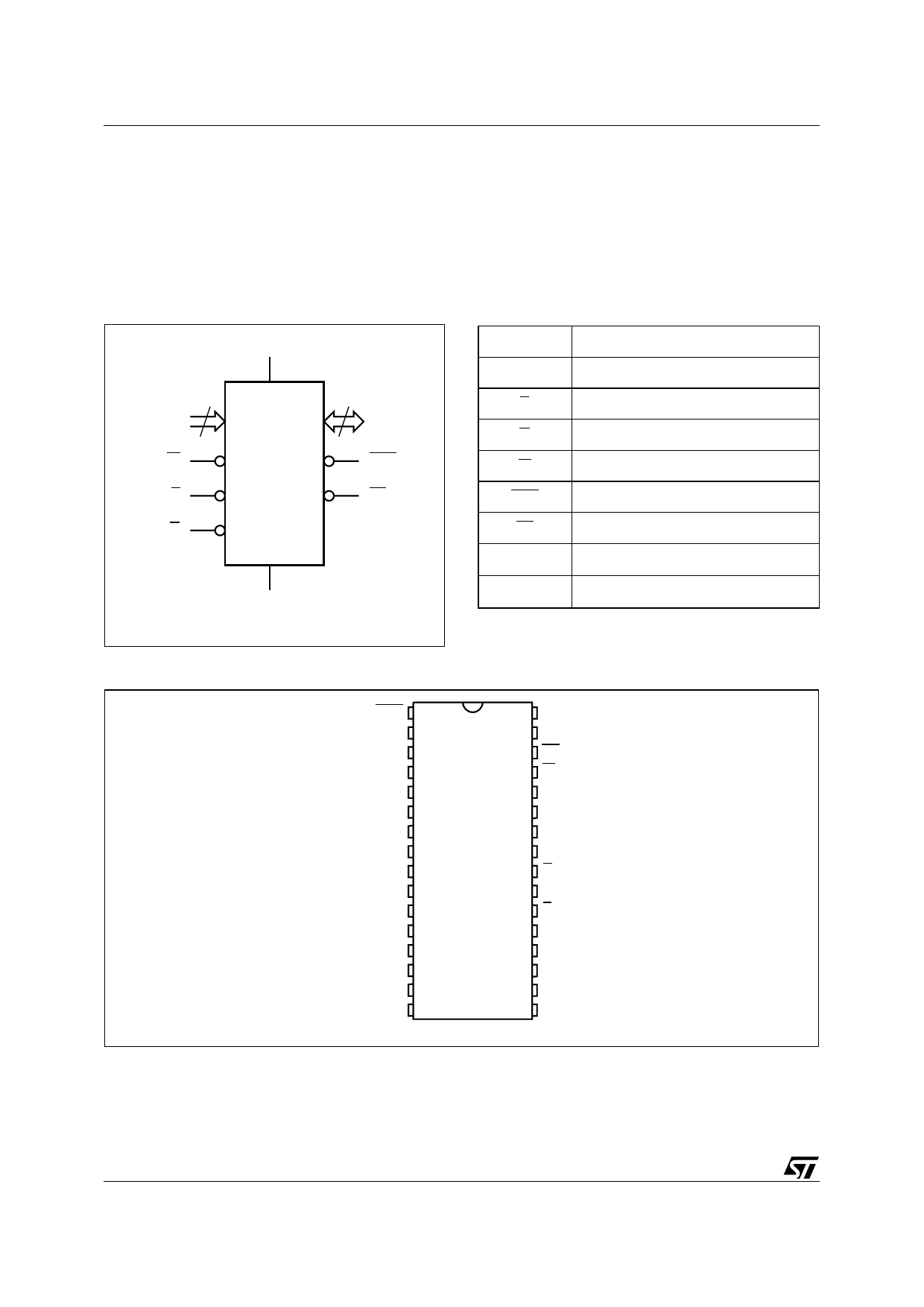

Figure 4. AC Testing Load Circuit

DEVICE

UNDER

TEST

650в„Ұ

CL = 100pF

or 50pF(1)

1.75V

CL includes JIG capacitance

AI03630

Note: 1. 50pF for M48Z129V (3.3V).

programmed time intervals of 24 hours. The Bat-

tery Low (BL) pin will be asserted if the battery volt-

age is found to be less than approximately 2.5V. If

a battery low is generated during a power-up se-

quence, this indicates that the battery is below 2.5

volts and may not be able to maintain data integrity

in the SRAM. Data should be considered suspect,

and verified as correct.

If a battery low indication is generated during the

24-hour interval check, this indicates that the bat-

tery is near end of life. However, data is not com-

promised due to the fact that a nominal VCC is

supplied.

The M48Z129Y/V only monitors the battery when

a nominal VCC is applied to the device. Thus ap-

plications which require extensive durations in the

battery back-up mode should be powered-up peri-

odically (at least once every few months) in order

for this technique to be beneficial. Additionally, if

a battery low is indicated, data integrity should be

verified upon power-up via a checksum or other

technique. The BL pin is an open drain output and

an appropriate pull-up resistor should be chosen

to control the rise time.

4/13