M48Z08(2010) жЯ•зЬЛжХЄжУЪи°®пЉИPDFпЉЙ - STMicroelectronics

йЫґдїґзЉЦеПЈ

дЇІеУБжППињ∞ (еКЯиГљ)

зФЯдЇІеОВеЃґ

M48Z08 Datasheet PDF : 20 Pages

| |||

Operation modes

M48Z08, M48Z18

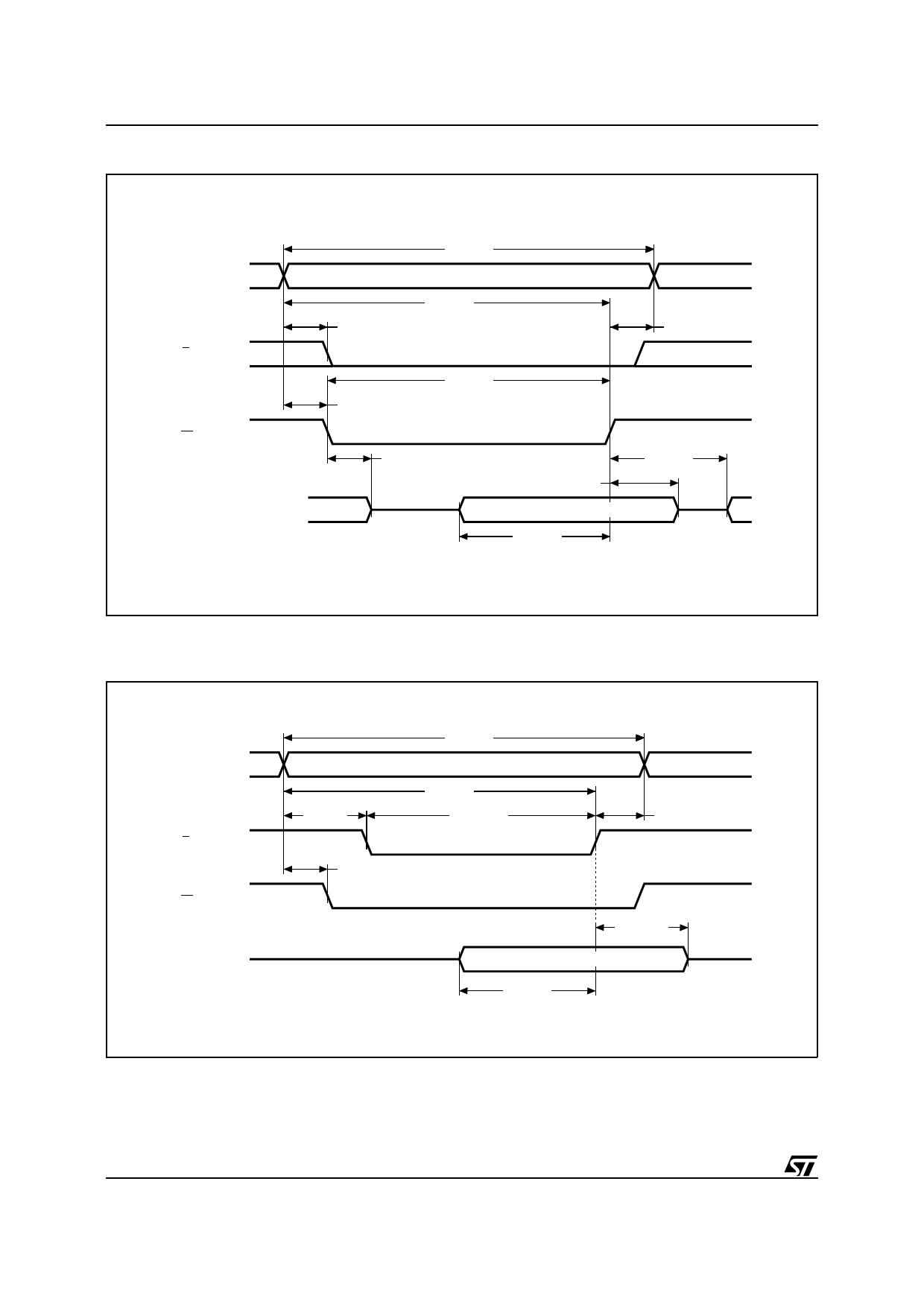

Figure 4. READ mode AC waveforms

A0-A12

E

G

DQ0-DQ7

tAVQV

tELQV

tAVAV

VALID

tELQX

tGLQV

tGLQX

tAXQX

tEHQZ

tGHQZ

VALID

AI01385

Note:

WRITE enable (W) = high.

Table 3. READ mode AC characteristics

Symbol

Parameter(1)

M48Z08/M48Z18

Unit

Min

Max

tAVAV

READ cycle time

100

ns

tAVQV

Address valid to output valid

100

ns

tELQV

Chip enable low to output valid

100

ns

tGLQV

tELQX(2)

tGLQX(2)

tEHQZ(2)

tGHQZ(2)

tAXQX

Output enable low to output valid

Chip enable low to output transition

Output enable low to output transition

Chip enable high to output Hi-Z

Output enable high to output Hi-Z

Address transition to output transition

50

ns

10

ns

5

ns

50

ns

40

ns

5

ns

1. Valid for ambient operating temperature: TA = 0 to 70 °C; VCC = 4.75 to 5.5 V or 4.5 to 5.5 V (except where noted).

2. CL = 30 pF.

2.2

WRITE mode

The M48Z08/18 is in the WRITE mode whenever W and E are active. The start of a WRITE

is referenced from the latter occurring falling edge of W or E.

A WRITE is terminated by the earlier rising edge of W or E. The addresses must be held

valid throughout the cycle. E or W must return high for a minimum of tEHAX from chip enable

or tWHAX from WRITE Enable prior to the initiation of another READ or WRITE cycle. Data-

in must be valid tDVWH prior to the end of WRITE and remain valid for tWHDX afterward. G

should be kept high during WRITE cycles to avoid bus contention; although, if the output bus

has been activated by a low on E and G, a low on W will disable the outputs tWLQZ after W

falls.

8/20

Doc ID 2424 Rev 7