M62320GP 查看數據表(PDF) - Renesas Electronics

零件编号

产品描述 (功能)

生产厂家

M62320GP Datasheet PDF : 11 Pages

| |||

M62320GP

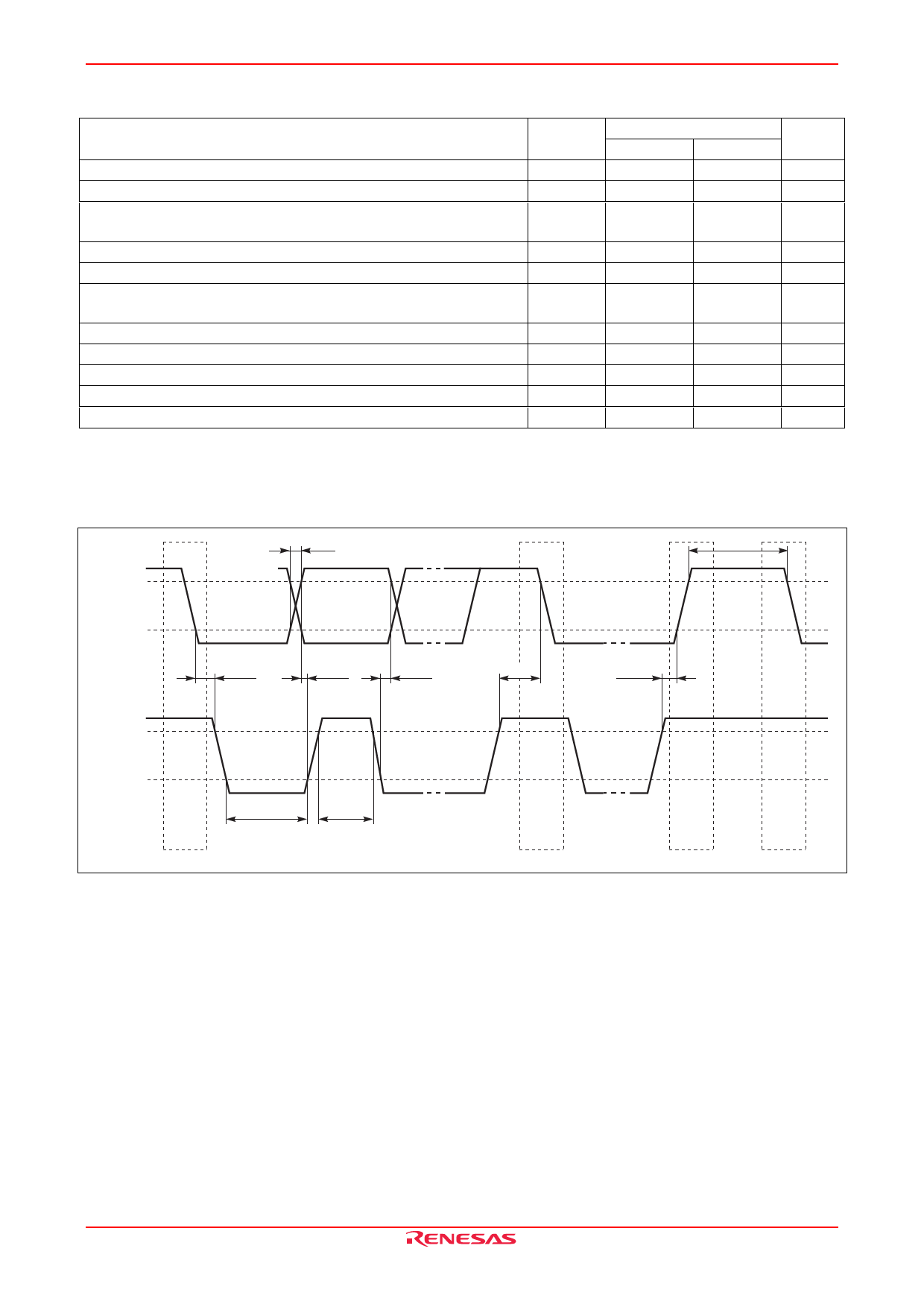

I2C BUS Characteristics

Limits

Item

Symbol

Min

Max

Unit

SCL clock frequency

fSCL

0

100

kHz

Free time: the bus must be free before a new transmission can start tBUF

4.7

—

μs

Hold time START Condition

tHD:STA

4.0

—

μs

After this period, the first clock pulse is generated.

Low period of the clock

High period of the clock

Set-up time for START condition

Only relevant for a repeated START condition

tLOW

4.7

tHIGH

4.0

tSU:STA

4.7

—

μs

—

μs

—

μs

Data Hold time

tHD:DAT

0

—

μs

Data Set-up time

tSU:DAT

250

—

ns

Rise time of SDA and SCL signals

tR

—

1000

ns

Fall time of SDA and SCL signals

Set-up time for STOP condition

tF

—

300

ns

tSU:STO

4.0

—

μs

Note: Transmitter must internally provide at least a hold time to bridge the undefined region (300 ns max) of the falling

edge of SCL.

Timing Chart

VIH

SDA

VIL

tHD:STA

tR, tF

tSU:DAT

tHD:DAT

tSU:STA

tBUF

tSU:STO

VIH

SCL

VIL

Start

tLOW

tHIGH

Start

Stop

Start

REJ03D0909-0100 Rev.1.00 Mar 25, 2008

Page 4 of 10