MAX690A(1993) 查看數據表(PDF) - Maxim Integrated

零件编号

产品描述 (功能)

生产厂家

MAX690A Datasheet PDF : 12 Pages

| |||

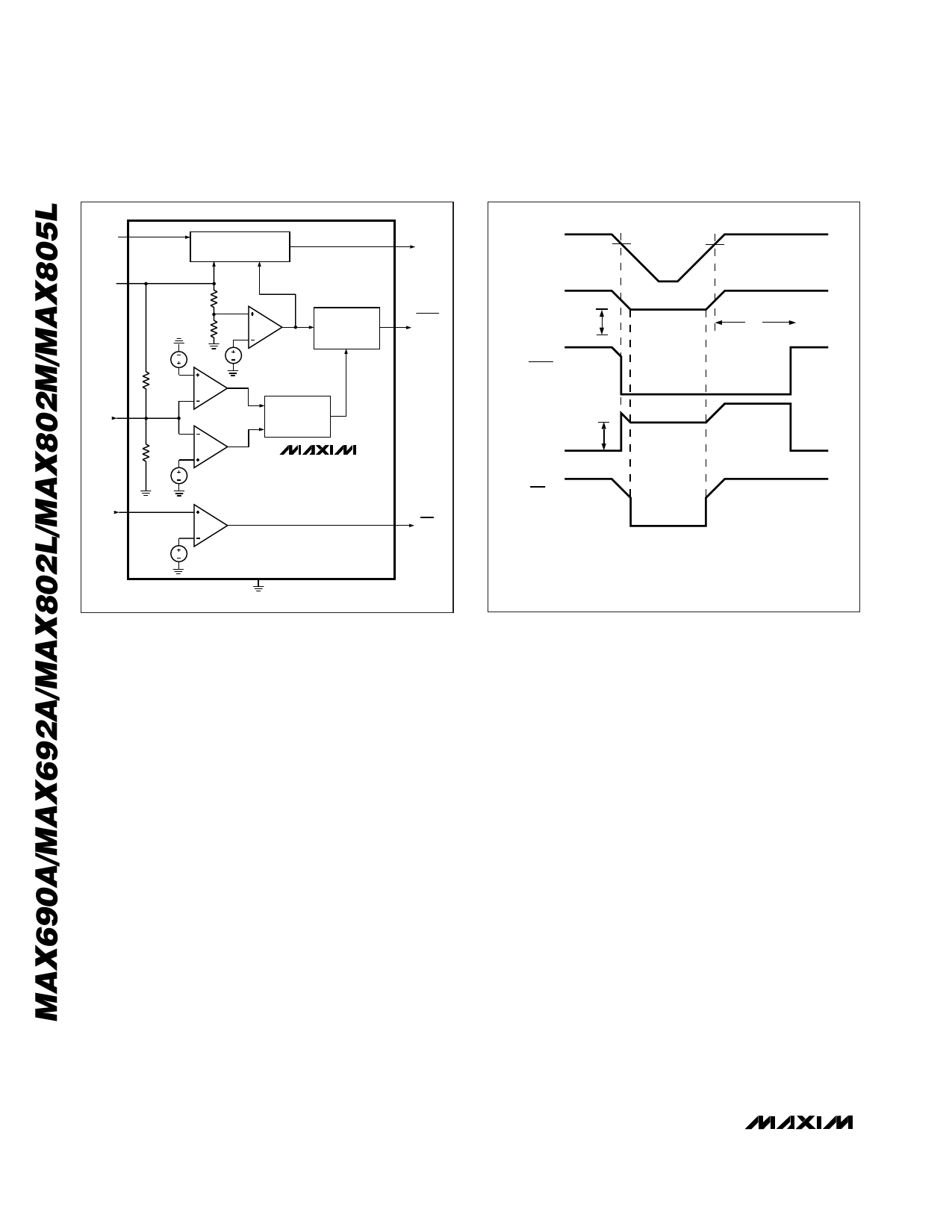

Microprocessor Supervisory Circuits

VBATT

VCC

BATTERY-SWITCHOVER

CIRCUITRY

VOUT

3.5V

1.25V

RESET

GENERATOR

RESET

(RESET)

WDI

WATCHDOG

TIMER

MAX690A

0.8V

MAX692A

MAX802L

MAX802M

PFI

MAX805L

PFO

1.25V

( ) ARE FOR MAX805L ONLY.

GND

Figure 1. Block Diagram

_______________Detailed Description

Reset Output

A microprocessor’s (µP’s) reset input starts the µP in a

known state. When the µP is in an unknown state, it should

be held in reset. The MAX690A/MAX692A/MAX802L/

MAX802M assert reset during power-up and prevent code

execution errors during power-down or brownout condi-

tions.

On power-up, once VCC reaches 1V, RESET is guaran-

teed to be a logic low. As VCC rises, RESET remains

low. When VCC exceeds the reset threshold, an internal

timer keeps RESET low for a time equal to the reset

pulse width; after this interval, RESET goes high (Figure

2). If a brownout condition occurs (if VCC dips below

the reset threshold), RESET is triggered. Each time

RESET is triggered, it stays low for the reset pulse width

interval. Any time VCC goes below the reset threshold,

the internal timer restarts the pulse. If a brownout con-

dition interrupts a previously initiated reset pulse, the

reset pulse continues for another 200ms. On power-

down, once VCC goes below the threshold, RESET is

guaranteed to be logic low until VCC droops below 1V.

RESET is also triggered by a watchdog timeout. If a

high or low is continuously applied to the WDI pin for

1.6sec, RESET pulses low. As long as RESET is assert-

+5V

VCC

0V

VOUT

3.0V

tRS

0V

+5V

RESET

0V

+5V

(RESET)

3.0V

0V

+5V

PFO

0V

( ) ARE FOR MAX805L ONLY.

VBATT = PFI = 3.0V

IOUT = 0mA

Figure 2. Timing Diagram

ed, the watchdog timer remains clear. When RESET

comes high, the watchdog resumes timing and must be

serviced within 1.6sec. If WDI is tied high or low, a

RESET pulse is triggered every 1.8sec (tWD plus tRS).

The MAX805L active-high RESET output is the inverse

of the MAX690A/MAX692A/MAX802L/MAX802M RESET

output, and is guaranteed to be valid with VCC down to

1.1V. Some µPs, such as Intel’s 80C51, require an

active-high reset pulse.

Watchdog Input

The watchdog circuit monitors the µP’s activity. If the

µP does not toggle the watchdog input (WDI) within

1.6sec, a reset pulse is triggered. The internal 1.6sec

timer is cleared by either a reset pulse or by open cir-

cuiting the WDI input. As long as reset is asserted or

the WDI input is open circuited, the timer remains

cleared and does not count. As soon as reset is

released or WDI is driven high or low, the timer starts

counting. It can detect pulses as short as 50ns.

Power-Fail Comparator

The PFI input is compared to an internal 1.25V refer-

ence. If PFI is less than 1.25V, PFO goes low. The

power-fail comparator is intended for use as an under-

voltage detector to signal a failing power supply; it

6 _______________________________________________________________________________________