MB95FV100D-101 查看數據表(PDF) - Fujitsu

零件编号

产品描述 (功能)

生产厂家

MB95FV100D-101 Datasheet PDF : 68 Pages

| |||

MB95160 Series

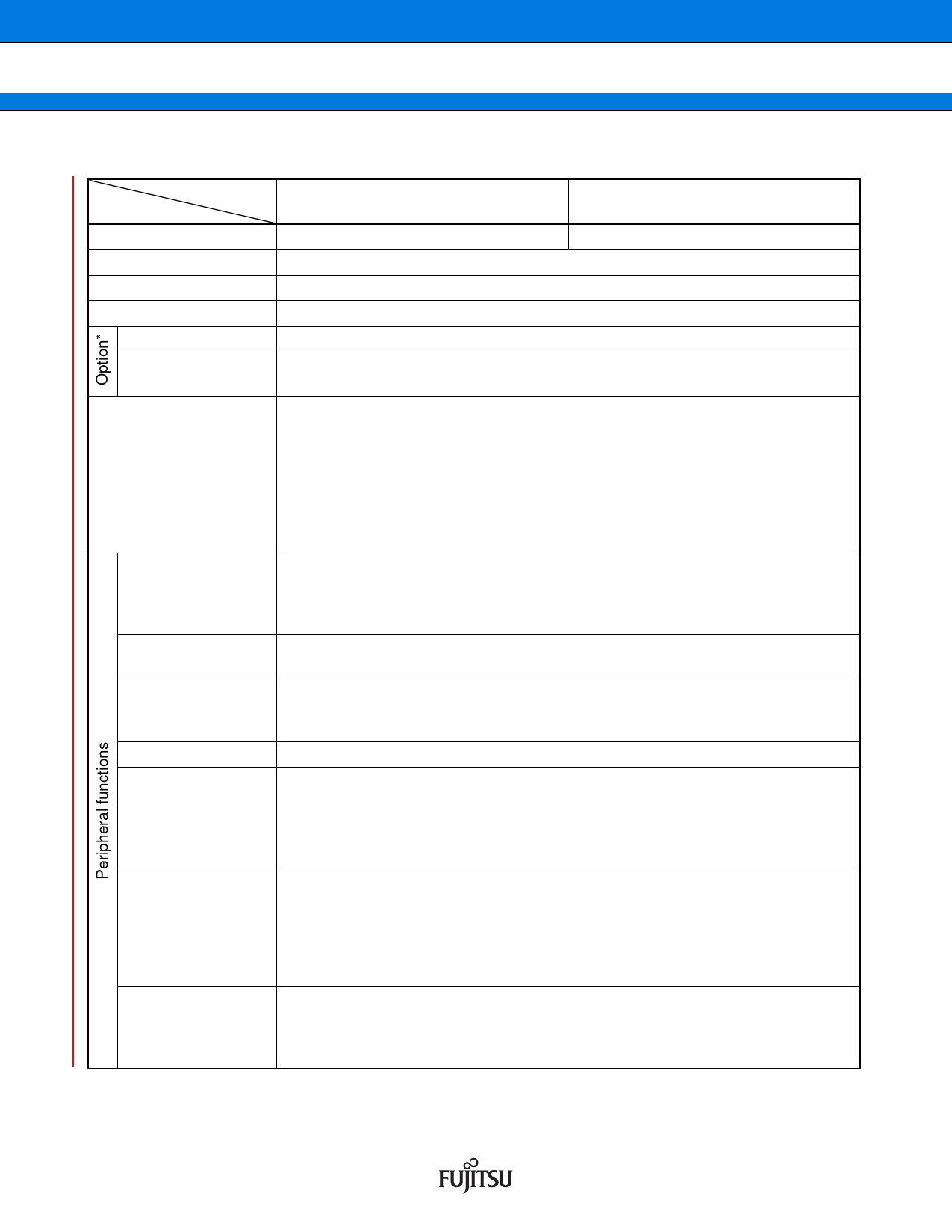

■ PRODUCT LINEUP

Part number

Parameter

MB95F166D

MB95166D

Type

Flash memory product

Mask ROM product

ROM capacity

32 Kbytes

RAM capacity

1 Kbyte

Reset output

No

Clock system

Dual clock

Low voltage

detection reset

No

CPU functions

Number of basic instructions

: 136

Instruction bit length

: 8 bits

Instruction length

: 1 to 3 bytes

Data bit length

: 1, 8, and 16 bits

Minimum instruction execution time : 61.5 ns (at machine clock frequency

16.25 MHz)

Interrupt processing time

: 0.6 μs (at machine clock frequency

16.25 MHz)

Ports (Max 53 ports)

General-purpose I/O port (N-ch open drain) : 2 ports

General-purpose I/O port (CMOS)

: 51 ports

Programmable input voltage levels of port.

CMOS input level/hysteresis input level.

Timebase timer

(1 channel)

Interrupt cycle : 0.5 ms, 2.1 ms, 8.2 ms, 32.8 ms (at main oscillation clock 4 MHz)

Watchdog timer

Reset generated cycle

At main oscillation clock 10 MHz

: Min 105 ms

At sub oscillation clock 32.768 kHz (for dual clock product) : Min 250 ms

Wild register

Capable of replacing 3 bytes of ROM data

I2C

(1 channel)

Master/slave sending and receiving

Bus error function and arbitration function

Detecting transmitting direction function

Start condition repeated generation and detection functions

Built-in wake-up function

UART/SIO

(1 channel)

Data transfer capable in UART/SIO

Full duplex double buffer,

variable data length (5/6/7/8-bit), built-in baud rate generator

NRZ type transfer format, error detected function

LSB-first or MSB-first can be selected.

Clock synchronous (SIO) or clock asynchronous (UART) serial data transfer capable

LIN-UART

(1 channel)

Dedicated reload timer allowing a wide range of communication speeds to be set.

Full duplex double buffer.

Capable of serial data transfer synchronous or asynchronous to clock signal.

LIN functions available as the LIN master or LIN slave.

(Continued)

DS07-12618-2E

3