MCIMX255AJM4A(2010) 查看數據表(PDF) - Freescale Semiconductor

零件编号

产品描述 (功能)

生产厂家

MCIMX255AJM4A

(Rev.:2010)

(Rev.:2010)

MCIMX255AJM4A Datasheet PDF : 134 Pages

| |||

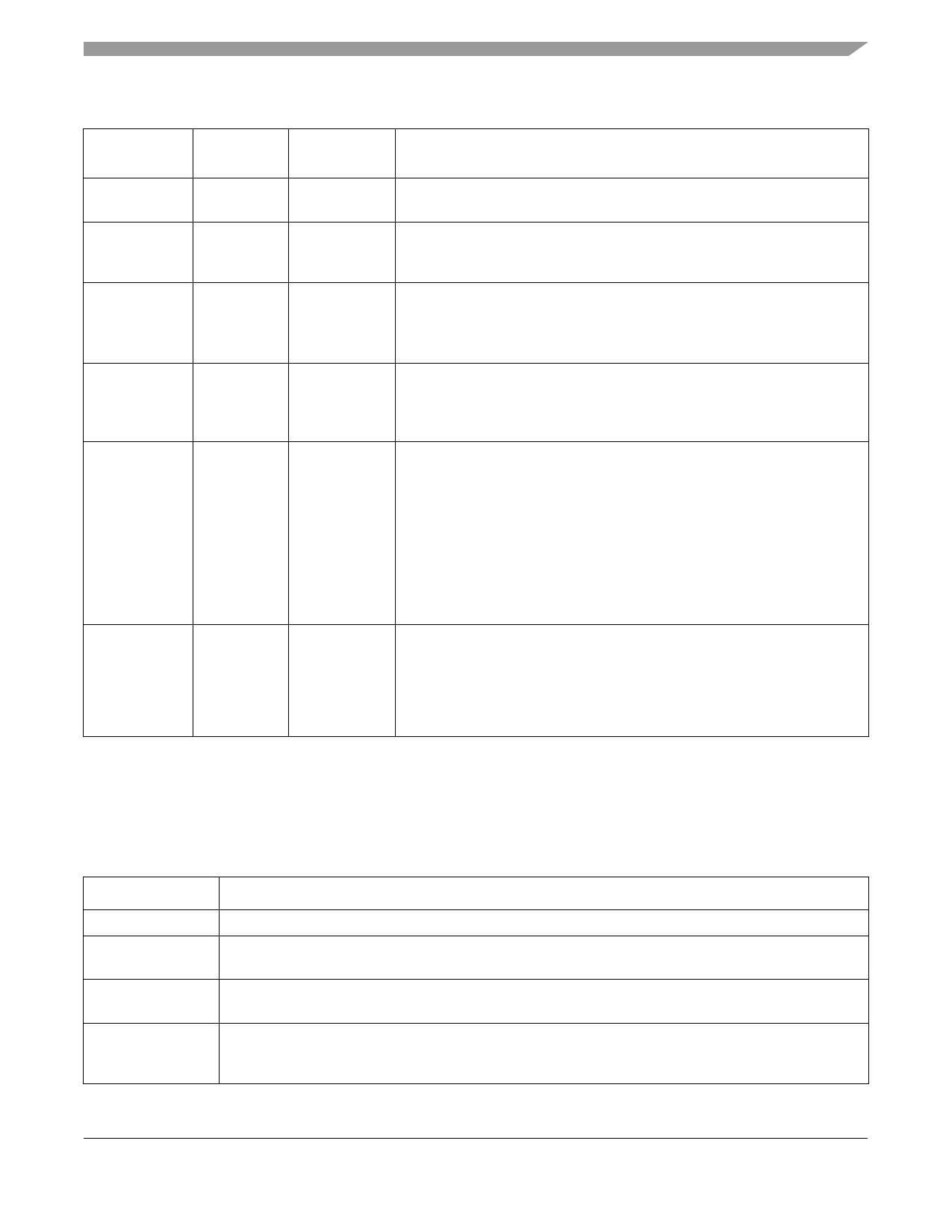

Table 3. i.MX25 Digital and Analog Modules (continued)

Block

Mnemonic

Block Name Subsystem

Brief Description

SSI(2)

I2S/SSI/AC97 Connectivity

interface

peripherals

TSC (and ADC) Touchscreen Multimedia

controller (and peripherals

A/D converter)

UART(5)

UART

interface

Connectivity

peripherals

USBOTG

USBHOST

High-speed

USB

on-the-go

Connectivity

peripherals

The SSI is a full-duplex serial port that allows the processor to communicate

with a variety of serial protocols, including the Freescale Semiconductor SPI

standard and the inter-IC sound bus standard (I2S). The SSIs

interface to the AUDMUX for flexible audio routing.

The touchscreen controller and associated Analog-to-Digital Converter

(ADC) together provide a resistive touchscreen solution. The module

implements simultaneous touchscreen control and auxiliary ADC operation

for temperature, voltage, and other measurement functions.

Each of the UART modules supports the following serial data

transmit/receive protocols and configurations:

• 7- or 8-bit data words, one or two stop bits, programmable parity (even,

odd, or none)

• Programmable baud rates up to 4 MHz. This is a higher maximum baud

rate than the 1.875 MHz specified by the TIA/EIA-232-F standard and

previous Freescale UART modules. 32-byte FIFO on Tx and 32 half-word

FIFO on Rx supporting auto-baud

• IrDA-1.0 support (up to SIR speed of 115200 bps)

• Option to operate as 8-pins full UART, DCE, or DTE

The USB module provides high-performance USB On-The-Go (OTG) and

host functionality (up to 480 Mbps), compliant with the USB 2.0 specification,

the OTG supplement, and the ULPI 1.0 Low Pin Count specification. The

module has DMA capabilities for handling data transfer between internal

buffers and system memory. An OTG HS PHY and HOST FS PHY are also

integrated.

2.1 Special Signal Considerations

Special signal considerations are listed in Table 4. The package contact assignment is found in Section 4,

“Package Information and Contact Assignment.” Signal descriptions are provided in the reference manual.

.

Table 4. Signal Considerations

Signal

Description

BAT_VDD

DryIce backup power supply input.

CLK0

Clock-out pin; renders the internal clock visible to users for debugging. The clock source is controllable

through CRM registers. This pin can also be configured (through muxing) to work as a normal GPIO.

CLK_SEL

Used to select the ARM clock source from MPLL out or from external EXT_ARMCLK. In normal operation,

CLK_SEL should be connected to GND.

EXT_ARMCLK

Primarily for Freescale factory use. There is no internal on-chip pull-up/down on this pin, so it must be

externally connected to GND or VDD. Aside from factory use, this pin can also be configured (through

muxing) to work as a normal GPIO.

MESH_C, MESH_D Wire-mesh tamper detect pins that can be routed at the PCB board to detect attempted tampering of a

protected wire. When security measures are implemented, MESH_C should be pulled-up or connected to

NVCC_DRYICE and triggers a tamper event when floating or when connected to MESH_D. MESH_D

should be pulled-down or connected to GND and triggers an event when floating or connected to

MESH_C. These pins can be left unconnected if the DryIce security features are not being used.

i.MX25 Applications Processor for Automotive Products, Rev. 5

Freescale Semiconductor

9