MSM80C85 查看數據表(PDF) - Oki Electric Industry

零件编号

产品描述 (功能)

生产厂家

MSM80C85 Datasheet PDF : 29 Pages

| |||

¡ Semiconductor

MSM80C85AHRS/GS/JS

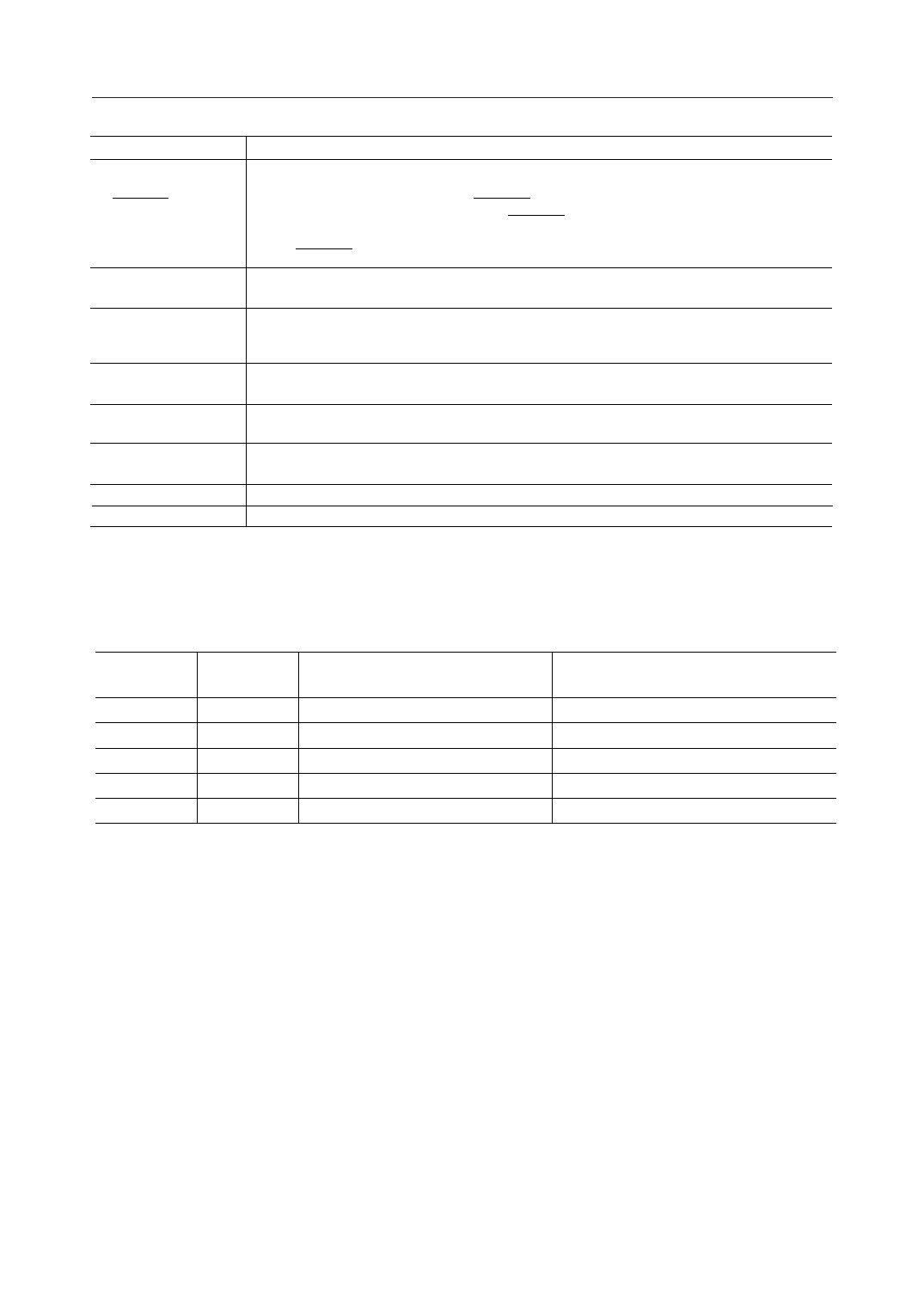

Symbol

RESET IN

(Input)

RESET OUT

(Output)

X1, X2

(Input)

CLK

(Output)

SID

(Input)

SOD

(Output)

VCC

GND

Function

Sets the Program Counter to zero and resets the Interrupt Enable and HLDA flip-flops and release

power down mode. The data and address buses and the control lines are 3-stated during RESET and

because of the asynchronous nature of RESET IN, the processor's internal registers and flags may be

altered by RESET with unpredictable results. RESET IN is a Schmitt-triggered input, allowing

connection to an R-C network for power-on RESET delay. The cpu is held in the reset condition as

long as RESET IN is applied.

Indicated cpu is being reset. Can be used as a system reset. The signal is synchronized to

the processor clock and lasts an integral number of clock periods.

X1 and X2 are connected to a crystal to drive the internal clock generator. X1 can also be an external

clock input from a logic gate. The input frequency is divided by 2 to give the processor's internal

operating frequency.

Clock Output for use as a system clock. The period of CLK is twice the X1, X2 input period.

Serial input data line. The data on this line is loaded into accumulator bit 7 whenever a RIM instruction

is executed.

Serial output data line. The output SOD is set or reset as specified by the SIM instruction.

+ 5 Volt supply

Ground Reference.

Name

TRAP

RST 7.5

RST 6.5

RST 5.5

INTR

Table 1 Interrupt Priority, Restart Address, and Sensitivity

Priority

1

2

3

4

5

Address Branched To (1)

When Interrupt Occurs

24H

3CH

34H

2CH

(2)

Type Trigger

Rising edge and high level unit sampled.

Rising edge (latched).

High level unitl sampled.

High level until sampled.

High level until sampled.

Notes: (1) The processor pushes the PC on the stack before branching to the indicated

address.

(2) The address branched to depends on the instruction provided to the cpu

when the interrupt is acknowledged.

5/29