CY7C1334 查看數據表(PDF) - Cypress Semiconductor

零件编号

产品描述 (功能)

生产厂家

CY7C1334 Datasheet PDF : 12 Pages

| |||

CY7C1334

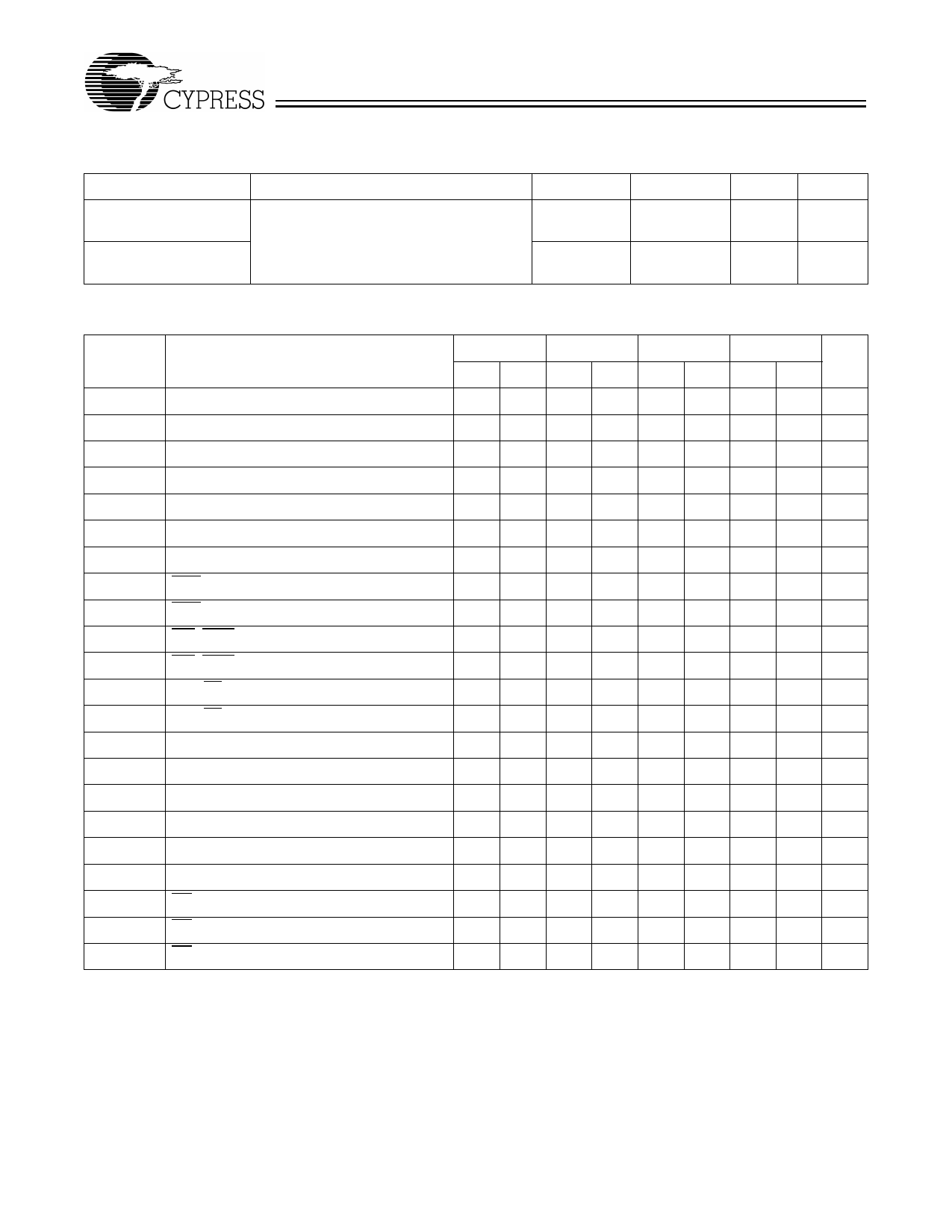

Thermal Resistance

Description

Test Conditions

Thermal Resistance

(Junction to Ambient)

Still Air, soldered on a 4.25 x 1.125 inch,

4-layer printed circuit board

Thermal Resistance

(Junction to Case)

Symbol

ΘJA

ΘJC

TQFP Typ.

28

Units

°C/W

Notes

13

4

°C/W

13

Switching Characteristics Over the Operating Range[14, 15, 16]

-133

-100

-80

-50

Parameter

Description

Min. Max. Min. Max. Min. Max. Min. Max. Unit

tCYC

Clock Cycle Time

7.5

10

12.5

20.0

ns

tCH

Clock HIGH

2.2

3.5

4.0

6.0

ns

tCL

Clock LOW

2.2

3.5

4.0

6.0

ns

tCO

Data Output Valid After CLK Rise

4.2

5.0

7.0

10.0 ns

tDOH

Data Output Hold After CLK Rise

1.5

1.5

1.5

1.5

ns

tAS

Address Set-Up Before CLK Rise

2.0

2.2

2.5

3.0

ns

tAH

Address Hold After CLK Rise

0.5

0.5

1.0

1.5

ns

tCENS

CEN Set-Up Before CLK Rise

2.0

2.2

2.5

3.0

ns

tCENH

CEN Hold After CLK Rise

0.5

0.5

1.0

1.5

ns

tWES

GW, BWS[3:0] Set-Up Before CLK Rise

2.0

2.2

2.5

3.0

ns

tWEH

GW, BWS[3:0] Hold After CLK Rise

0.5

0.5

1.0

1.5

ns

tALS

ADV/LD Set-Up Before CLK Rise

2.0

2.2

2.5

3.0

ns

tALH

ADV/LD Hold after CLK Rise

0.5

0.5

1.0

1.5

ns

tDS

Data Input Set-Up Before CLK Rise

1.7

2.0

2.5

3.0

ns

tDH

Data Input Hold After CLK Rise

0.5

0.5

1.0

1.5

ns

tCES

Chip Enable Set-Up Before CLK Rise

2.0

2.2

2.5

3.0

ns

tCEH

tCHZ

tCLZ

tEOHZ

tEOLZ

tEOV

Chip Enable Hold After CLK Rise

Clock to High-Z[13, 15, 16, 17]

Clock to Low-Z[13, 15, 16, 17]

OE HIGH to Output High-Z[13, 15, 16, 17]

OE LOW to Output Low-Z[13, 15, 16, 17]

OE LOW to Output Valid[15]

0.5

0.5

1.0

1.5

ns

1.5 3.5 1.5 3.5 1.5 3.5 1.5 3.5 ns

1.5

1.5

1.5

1.5

ns

4.2

5.0

6.0

6.0 ns

1.0

1.0

1.0

1.0

ns

4.2

5.0

6.0

6.0 ns

Notes:

15. tCHZ, tCLZ, tOEV, tEOLZ, and tEOHZ are specified with A/C test conditions shown in part (a) of AC Test Loads. Transition is measured ± 200 mV from steady-state

voltage.

16. At any given voltage and temperature, tEOHZ is less than tEOLZ and tCHZ is less than tCLZ to eliminate bus contention between SRAMs when sharing the same

data bus. These specifications do not imply a bus contention condition, but reflect parameters guaranteed over worst case user conditions. Device is designed

to achieve High-Z prior to Low-Z under the same system conditions.

17. This parameter is sampled and not 100% tested.

Document #: 38-05065 Rev. **

Page 8 of 12