NJU26123V 查看數據表(PDF) - Japan Radio Corporation

零件编号

产品描述 (功能)

生产厂家

NJU26123V Datasheet PDF : 19 Pages

| |||

NJU26123

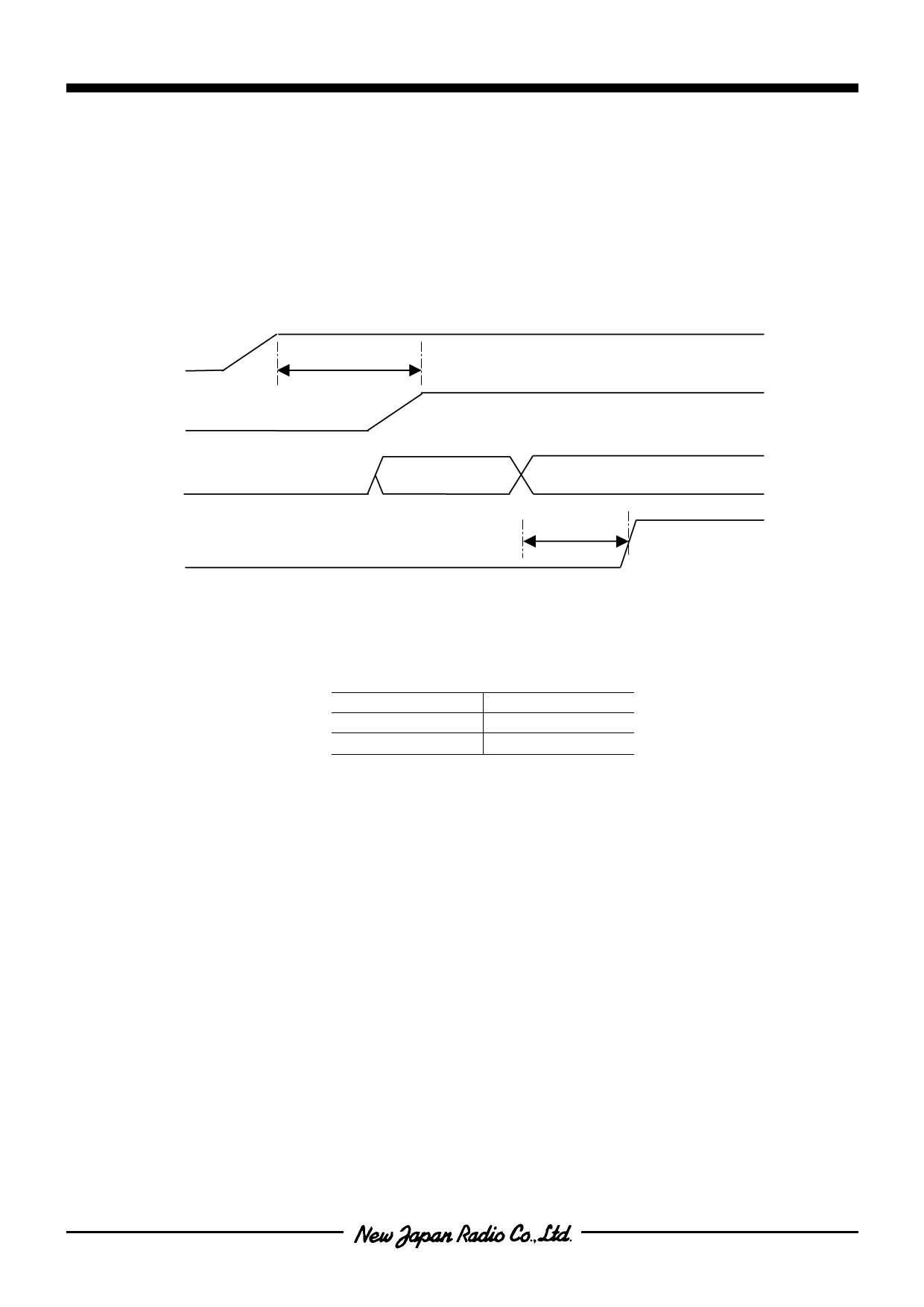

1.4 Reset

To initialize the NJU26123, RESETb pin should be set Low level during some period. After some period of

Low level, RESETb pin should be High level. This procedure starts the initialization of the NJU26123. After

the power supply and the oscillation of the NJU26123 becomes stable, RESETb pin must be kept

Low-level more than tRESETb period. (Fig.5)

After RESETb pin level goes to "High" (after reset release), a setup of the internal hardware of a Serial

Host Interface completes NJU26123 within 10msec. Then, it will be in the state which can communicate.

VDD

VREGO

CLK

tVREGO

OSC unstable

OSC stable

RESETb

Fig.5 Reset Timing

tRESETb

Table 4 Reset Time

Symbol

Time

tVREGO

tRESETb

≥ 10msec

≥ 1.0msec

Note :

Don’t stop the supply of a clock while operating. NJU26123 installs PLL circuit internally. If the supply of a

clock is stopped, PLL circuit cannot be sent a clock to the inside and NJU26123 does not operate normally.

If supply of a clock is stopped or the NJU26123 is reset again, putting a normal clock into CLK terminal, the

period RESETb terminal of tRESETb is kept “Low” level.(Table 4) Next, the NJU26123 is reset. Then redo

from initial setting.

-8-

Ver.2008-04-17