MSM80C88A-10GS-K 查看數據表(PDF) - Oki Electric Industry

零件编号

产品描述 (功能)

生产厂家

MSM80C88A-10GS-K Datasheet PDF : 37 Pages

| |||

¡ Semiconductor

MSM80C88A-10RS/GS/JS

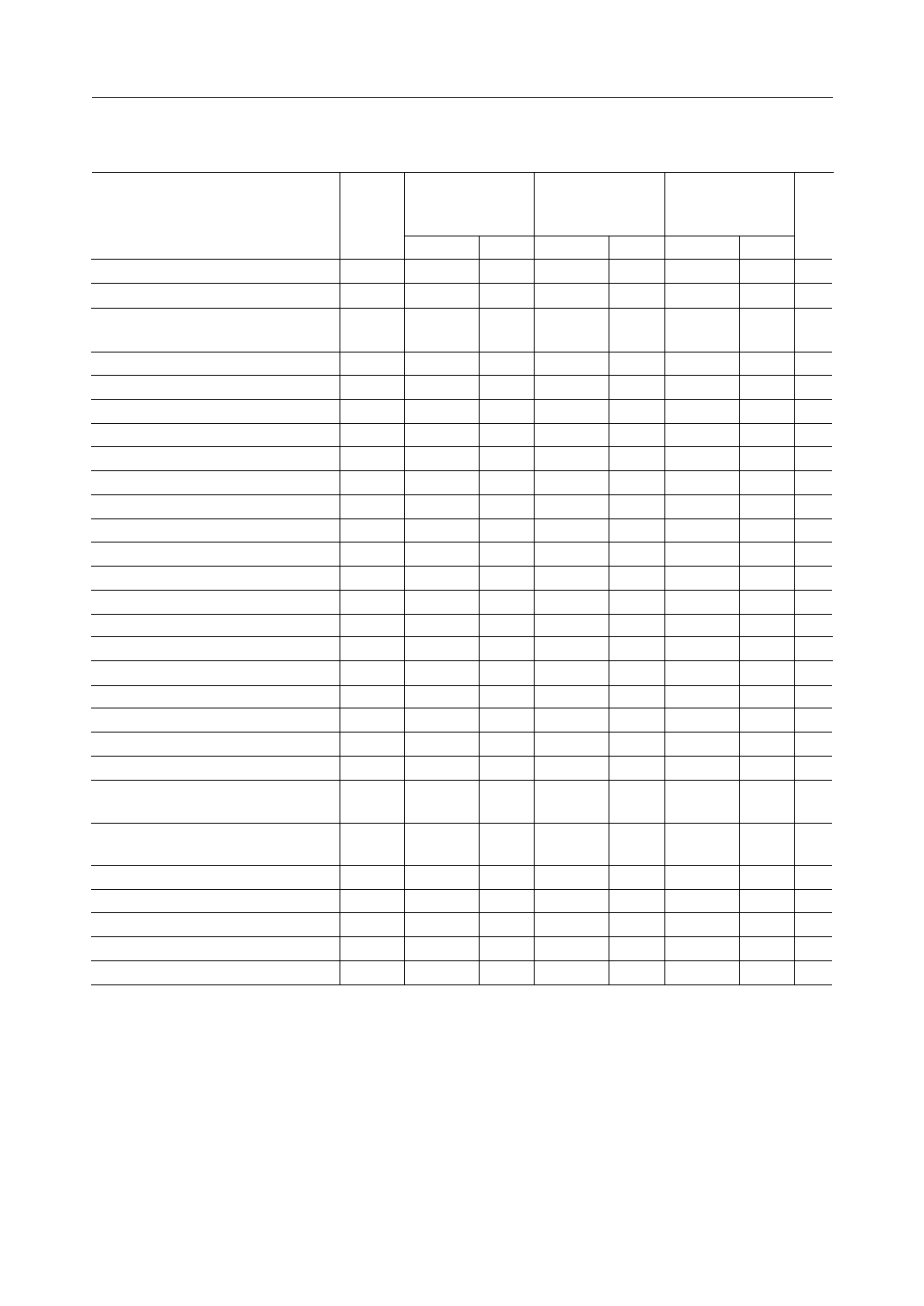

Timing Responses

Parameter

5 MHz Spec.

8 MHz Spec.

10 MHz Spec.

Symbol VCC = 4.5 V to 5.5 V VCC = 4.75 V to 5.25 V VCC = 4.75 V to 5.25 V Unit

Ta = –40 to +85°C Ta = 0 to +70°C Ta = 0 to +70°C

Command Active Delay (See Note 1) tCLML

Command Inactive Delay (See Note 1) tCLMH

READY Active to Status Passive

(See Note 4)

tRYHSH

Min.

5

5

—

Max.

45

45

110

Min.

5

5

—

Max.

35

45

65

Min.

5

5

—

Max.

35 ns

45 ns

45 ns

Status Active Delay

tCHSV

10

110

10

60

10

45 ns

Status Inactive Delay

tCLSH

10

130

10

70

10

60 ns

Address Valid Delay

tCLAV

10

110

10

60

10

60 ns

Address Hold Time

tCLAX

10

—

10

—

10

— ns

Address Float Delay

tCLAZ

tCLAX

80

tCLAX

50

tCLAX

50 ns

Status Valid to ALE High (See Note 1) tSVLH

—

35

—

25

—

25 ns

Status Valid to MCE High (See Note 1) tSVMCH

—

35

—

30

—

30 ns

CLK Low to ALE Valid (See Note 1) tCLLH

—

35

—

25

—

25 ns

CLK Low to MCE High (See Note 1) tCLMCH

—

35

—

25

—

25 ns

ALE Inactive Delay (See Note 1)

tCHLL

4

35

4

25

4

25 ns

Data Valid Delay

tCLDV

10

110

10

60

10

60 ns

Data Hold Time

tCHDX

10

—

10

—

10

— ns

Control Active Delay (See Note 1)

tCVNV

5

45

5

45

5

45 ns

Control Inactive Delay (See Note 1) tCVNX

5

45

5

45

5

45 ns

Address Float to RD Active

tAZRL

0

—

0

—

0

— ns

RD Active Delay

tCLRL

10

165

10

100

10

70 ns

RD Inactive Delay

tCLRH

10

150

10

80

10

60 ns

RD Inactive to Next Address Active

tRHAV tCLCL-45 — tCLCL-40 — tCLCL-35 — ns

Direction Control Active Delay

(See Note 1)

tCHDTL

—

50

—

50

—

50 ns

Direction Control Inactive Delay

(See Note 1)

tCHDTH

—

35

—

30

—

30 ns

GT Active Delay (See Note 5)

tCLGL

0

85

0

50

0

45 ns

GT Inactive Delay

tCLGH

0

85

0

50

0

45 ns

RD Width

tRLRH 2tCLCL-75 — 2tCLCL-50 — 2tCLCL-40 — ns

Output Rise Time (From 0.8 V to 2.0 V) tOLOH

—

15

—

15

—

15 ns

Output Fall Time (From 2.0 V to 0.8 V) tOHOL

—

15

—

15

—

15 ns

Notes: 1. Signals at MSM82C84A-2 or MSM82C88-2 are shown for reference only.

2. Setup requirement for asynchronous signal only to guarantee recognition at next

CLK.

3. Applies only to T2 state (8 ns into T3)

4. Applies only to T3 and wait states.

5. CL = 40 pF (RQ/GT0, RQ/GT1)

9/37