PCA9500 查看數據表(PDF) - NXP Semiconductors.

零件编号

产品描述 (功能)

生产厂家

PCA9500 Datasheet PDF : 26 Pages

| |||

NXP Semiconductors

PCA9500

8-bit I2C-bus and SMBus I/O port with 2-kbit EEPROM

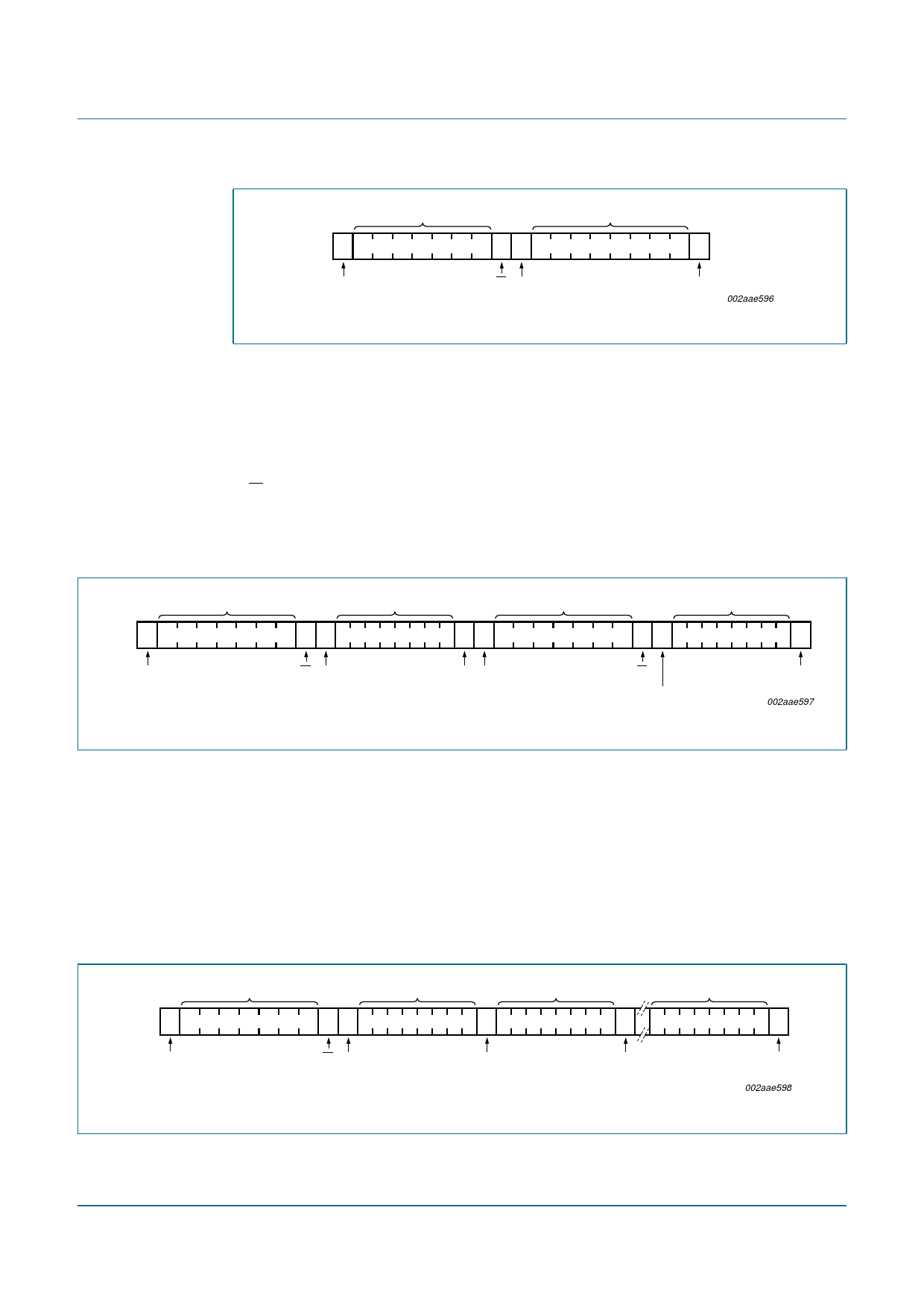

slave address (memory)

data from memory

SDA S 1 0 1 0 A2 A1 A0 1 A

P

START condition

Fig 12. Current address read

R/W acknowledge

from slave

STOP condition

002aae596

7.4.2.2 Random read

The PCA9500's random read mode allows the address to be read from to be specified by

the master. This is done by performing a dummy write to set the address counter to the

location to be read. The master must perform a byte write to the address location to be

read, but instead of transmitting the data after receiving the acknowledge from the

PCA9500, the master re-issues the START condition and memory slave address with the

R/W bit set to one. The PCA9500 will then transmit an acknowledge and use the next

eight clock cycles to transmit the data contained in the addressed location. The master

ceases the transmission by issuing the STOP condition after the eighth bit, omitting the

ninth clock cycle acknowledge.

slave address (memory)

SDA S 1 0 1 0 A2 A1 A0 0 A

word address

slave address (memory)

data from memory

A S 1 0 1 0 A2 A1 A0 1 A

P

START condition

Fig 13. Random read

R/W acknowledge acknowledge START condition

from slave

from slave

R/W

acknowledge

from slave

STOP

condition

002aae597

7.4.2.3 Sequential read

The PCA9500 sequential read is an extension of either the current address read or

random read. If the master does not issue a STOP condition after it has received the

eighth data bit, but instead issues an acknowledge, the PCA9500 will increment the

address counter and use the next eight cycles to transmit the data from that location. The

master can continue this process to read the contents of the entire memory. Upon

reaching address 255 the counter will return to address 0 and continue transmitting data

until a STOP condition is received. The master ceases the transmission by issuing the

STOP condition after the eighth bit, omitting the ninth clock cycle acknowledge.

slave address (memory)

data from memory

data from memory

SDA S 1 0 1 0 A2 A1 A0 1 A

DATA n

A

DATA n + 1

A

START condition

R/W acknowledge acknowledge

from slave

from master

acknowledge

from master

Fig 14. Sequential read

data from memory

DATA n + X

P

STOP

condition

002aae598

PCA9500_4

Product data sheet

Rev. 04 — 15 April 2009

© NXP B.V. 2009. All rights reserved.

9 of 26