PCA9554C 查看數據表(PDF) - NXP Semiconductors.

零件编号

产品描述 (功能)

生产厂家

PCA9554C

PCA9554C Datasheet PDF : 36 Pages

| |||

NXP Semiconductors

PCA9554B; PCA9554C

Low-voltage 8-bit I2C-bus/SMBus low power I/O port

6.4.4 Configuration register (03h)

The Configuration register (register 3) configures the direction of the I/O pins. If a bit in this

register is set to 1, the corresponding port pin is enabled as a high-impedance input. If a

bit in this register is cleared to 0, the corresponding port pin is enabled as an output.

Table 9. Configuration register (address 03h)

Bit

7

6

5

4

3

2

1

0

Symbol

C7

C6

C5

C4

C3

C2

C1

C0

Default

1

1

1

1

1

1

1

1

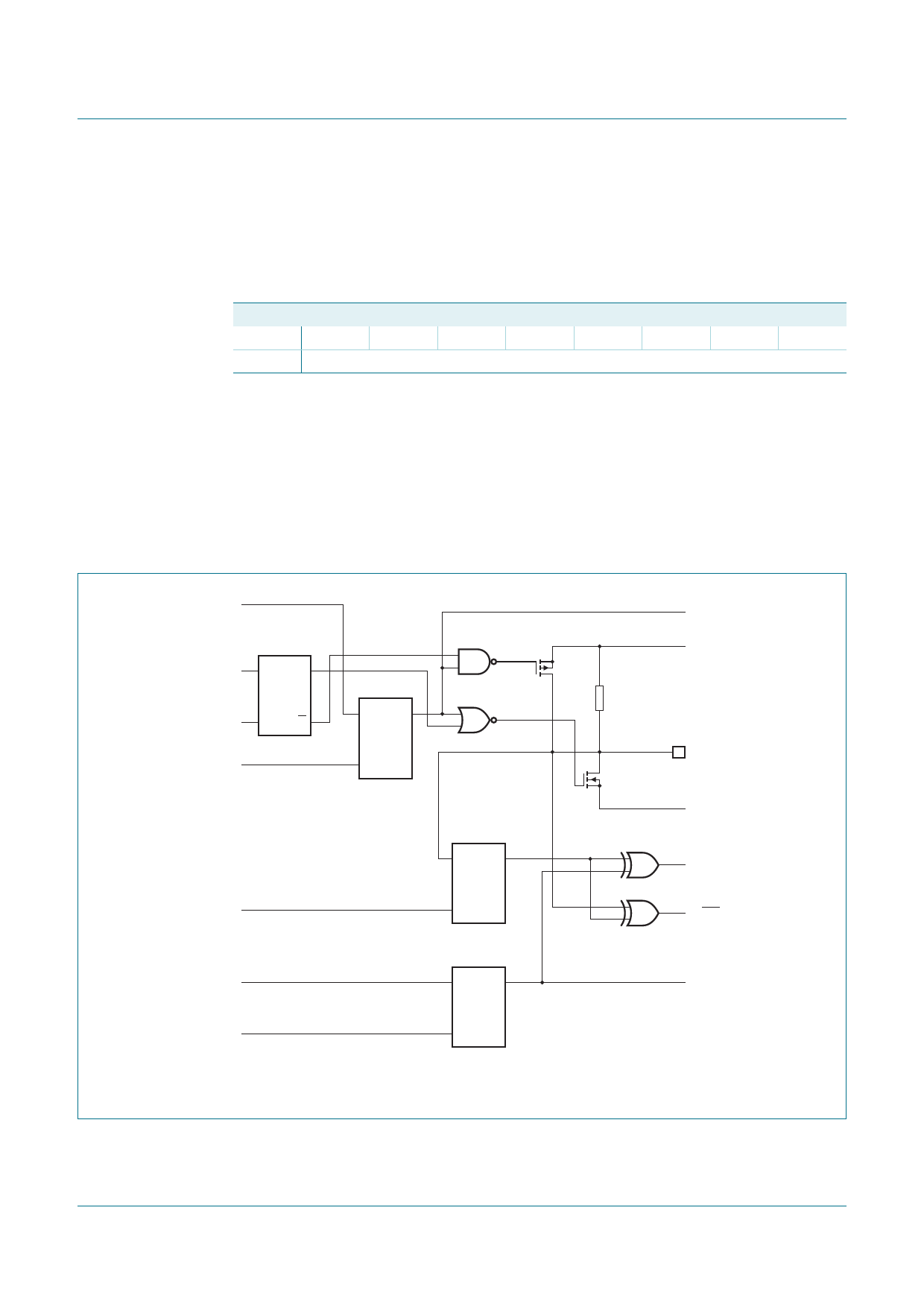

6.5 I/O port

When an I/O is configured as an input, FETs Q1 and Q2 are off, which creates a

high-impedance input. The input voltage may be raised above VDD to a maximum of 5.5 V.

If the I/O is configured as an output, Q1 or Q2 is enabled, depending on the state of the

Output port register. In this case, there are low-impedance paths between the I/O pin and

either VDD or VSS. The external voltage applied to this I/O pin should not exceed the

recommended levels for proper operation.

data from

shift register

data from

shift register

write configuration

pulse

configuration

register

D

Q

FF

CK Q

write pulse

D

Q

FF

CK

output port

register

read pulse

data from

shift register

write polarity

pulse

Q1

100 kΩ

Q2

input port

register

D

Q

FF

CK

polarity inversion

register

D

Q

FF

CK

On power-up or reset, all registers return to default values.

Fig 6. Simplified schematic of the I/Os (P0 to P7)

output port

register data

VDD

P0 to P7

VSS

input port

register data

to INT

polarity inversion

register data

002aah123

PCA9554B_PCA9554C

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 1 — 19 September 2012

© NXP B.V. 2012. All rights reserved.

7 of 36