IN74HC165N 查看數據表(PDF) - Integral Corp.

零件编号

产品描述 (功能)

生产厂家

IN74HC165N Datasheet PDF : 7 Pages

| |||

IN74HC165

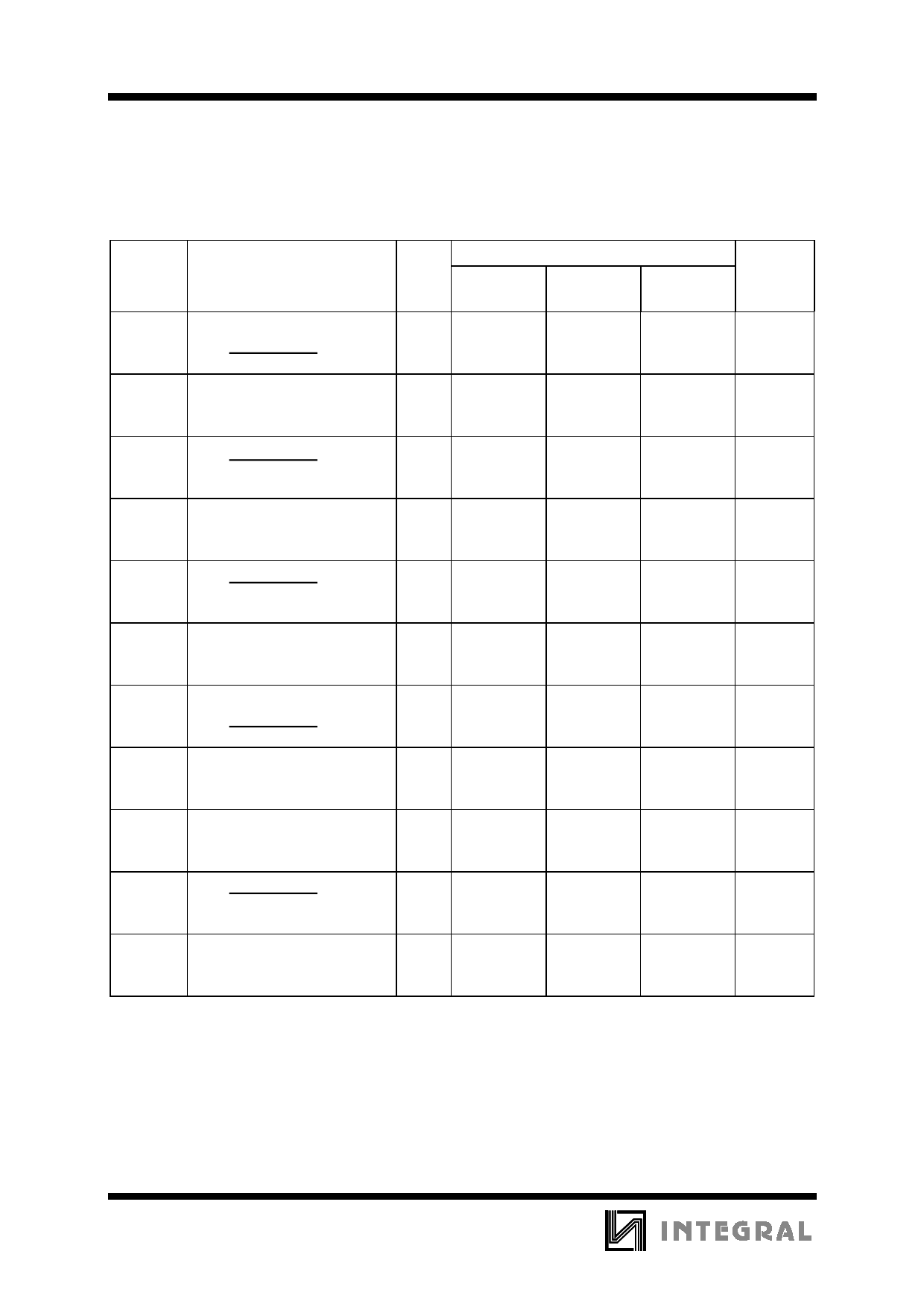

TIMING REQUIREMENTS (CL=50pF,Input tr=tf=6.0 ns)

Symbol

Parameter

VCC

Guaranteed Limit

V

25 °C to

≤85°C

≤125°C

Unit

-55°C

tSU

Minimum Setup Time, Parallel 2.0

100

125

150

ns

Data Inputs to Serial

4.5

20

25

30

Shift/Parallel Load (Figure 4) 6.0

17

21

26

tSU

Minimum Setup Time, Input

2.0

100

125

150

ns

SA to Clock (or Clock Inhibit) 4.5

20

25

30

(Figure 5)

6.0

17

21

26

tSU

Minimum Setup Time, Serial

2.0

100

125

150

ns

Shift/Parallel Load to Clock

4.5

20

25

30

(or Clock Inhibit) (Figure 6)

6.0

17

21

26

tSU

Minimum Setup Time, Clock

2.0

100

125

150

ns

to Clock Inhibit (Figure 7)

4.5

20

25

30

6.0

17

21

26

th

Minimum Hold Time, Serial

2.0

5

5

5

ns

Shift/Parallel Load to Parallel 4.5

5

5

5

Data Inputs (Figure 4)

6.0

5

5

5

th

Minimum Hold Time, Clock

2.0

5

5

5

ns

(or Clock Inhibit) to Input SA 4.5

5

5

5

(Figure 5)

6.0

5

5

5

th

Minimum Hold Time, Clock

2.0

5

5

5

ns

(or Clock Inhibit) to Serial

4.5

5

5

5

Shift/Parallel Load (Figure 6) 6.0

5

5

5

trec

Minimum Recovery Time,

2.0

100

125

150

ns

Clock to Clock Inhibit

4.5

20

25

30

(Figure 7)

6.0

17

21

26

tw

Minimum Pulse Width, Clock 2.0

80

(or Clock Inhibit) (Figure 1)

4.5

16

6.0

14

100

120

ns

20

24

17

20

tw

Minimum Pulse Width, Serial 2.0

80

Shift/Parallel Load (Figure 2) 4.5

16

6.0

14

100

120

ns

20

24

17

20

tr, tf Maximum Input Rise and Fall 2.0

1000

1000

1000

ns

Times (Figure 1)

4.5

500

500

500

6.0

400

400

400

232