PSD9342V10JT 查看數據表(PDF) - STMicroelectronics

零件编号

产品描述 (功能)

生产厂家

PSD9342V10JT

PSD9342V10JT Datasheet PDF : 89 Pages

| |||

PSD834F2V

In-System Programming (ISP)

Using the JTAG signals on Port C, the entire PSD

device can be programmed or erased without the

use of the MCU. The primary Flash memory can

also be programmed in-system by the MCU exe-

cuting the programming algorithms out of the sec-

ondary memory, or SRAM. The secondary

memory can be programmed the same way by ex-

ecuting out of the primary Flash memory. The PLD

or other PSD Configuration blocks can be pro-

grammed through the JTAG port or a device pro-

grammer. Table 3 indicates which programming

methods can program different functional blocks

of the PSD.

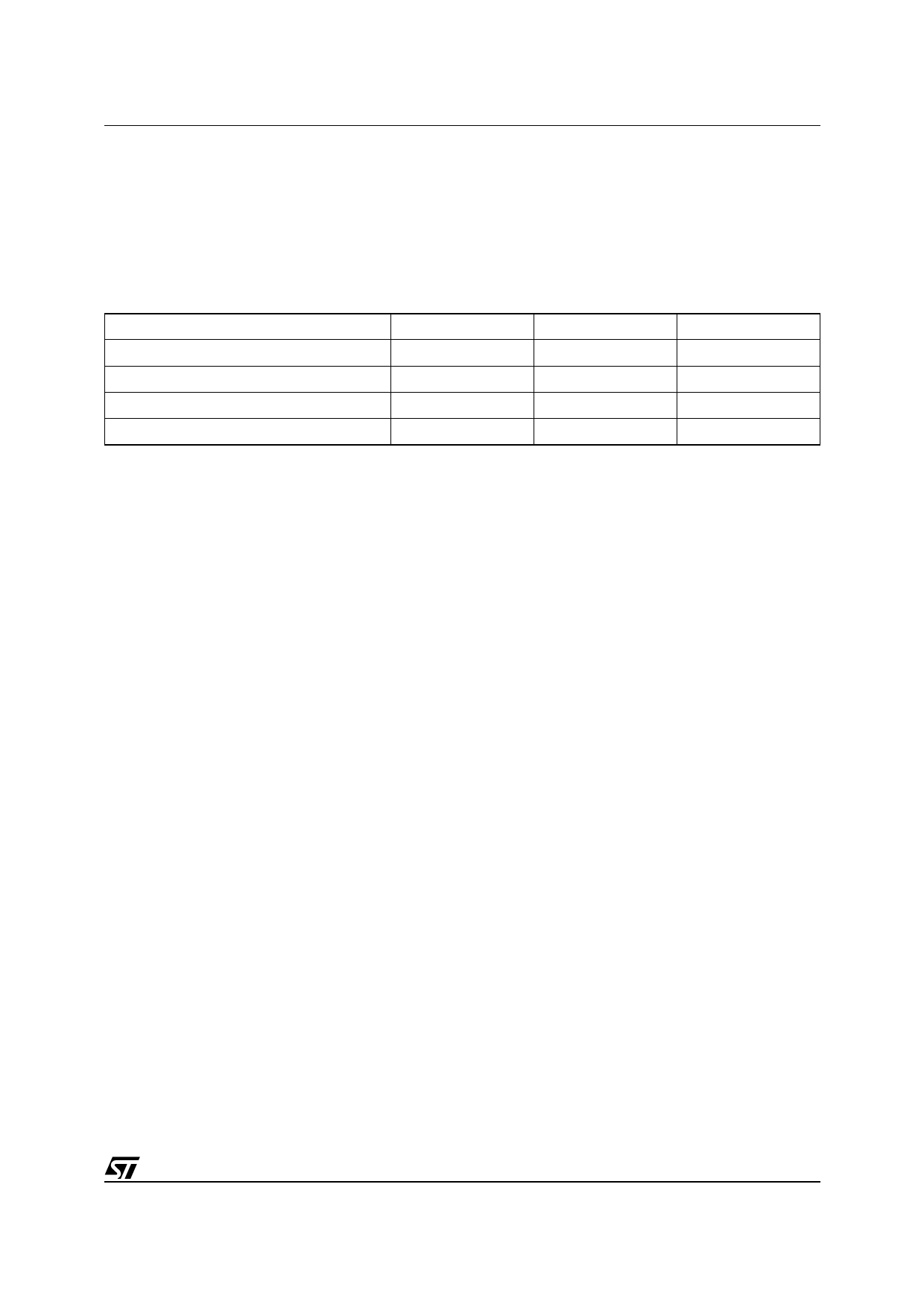

Table 3. Methods of Programming Different Functional Blocks of the PSD

Functional Block

JTAG Programming Device Programmer

IAP

Primary Flash Memory

Yes

Yes

Yes

Secondary Flash Memory

Yes

Yes

Yes

PLD Array (DPLD and CPLD)

Yes

Yes

No

PSD Configuration

Yes

Yes

No

Power Management Unit (PMU)

The Power Management Unit (PMU) gives the

user control of the power consumption on selected

functional blocks based on system requirements.

The PMU includes an Automatic Power-down

(APD) Unit that turns off device functions during

MCU inactivity. The APD Unit has a Power-down

mode that helps reduce power consumption.

The PSD also has some bits that are configured at

run-time by the MCU to reduce power consump-

tion of the CPLD. The Turbo bit in PMMR0 can be

reset to 0 and the CPLD latches its outputs and

goes to sleep until the next transition on its inputs.

Additionally, bits in PMMR2 can be set by the

MCU to block signals from entering the CPLD to

reduce power consumption. Please see the sec-

tion entitled “Power Management” on page 55 for

more details.

9/89