RA8825 查看數據表(PDF) - RAIO

零件编号

产品描述 (功能)

生产厂家

RA8825 Datasheet PDF : 6 Pages

| |||

Preliminary Version 1.1

RA8825

128x33 Graphic LCD Driver

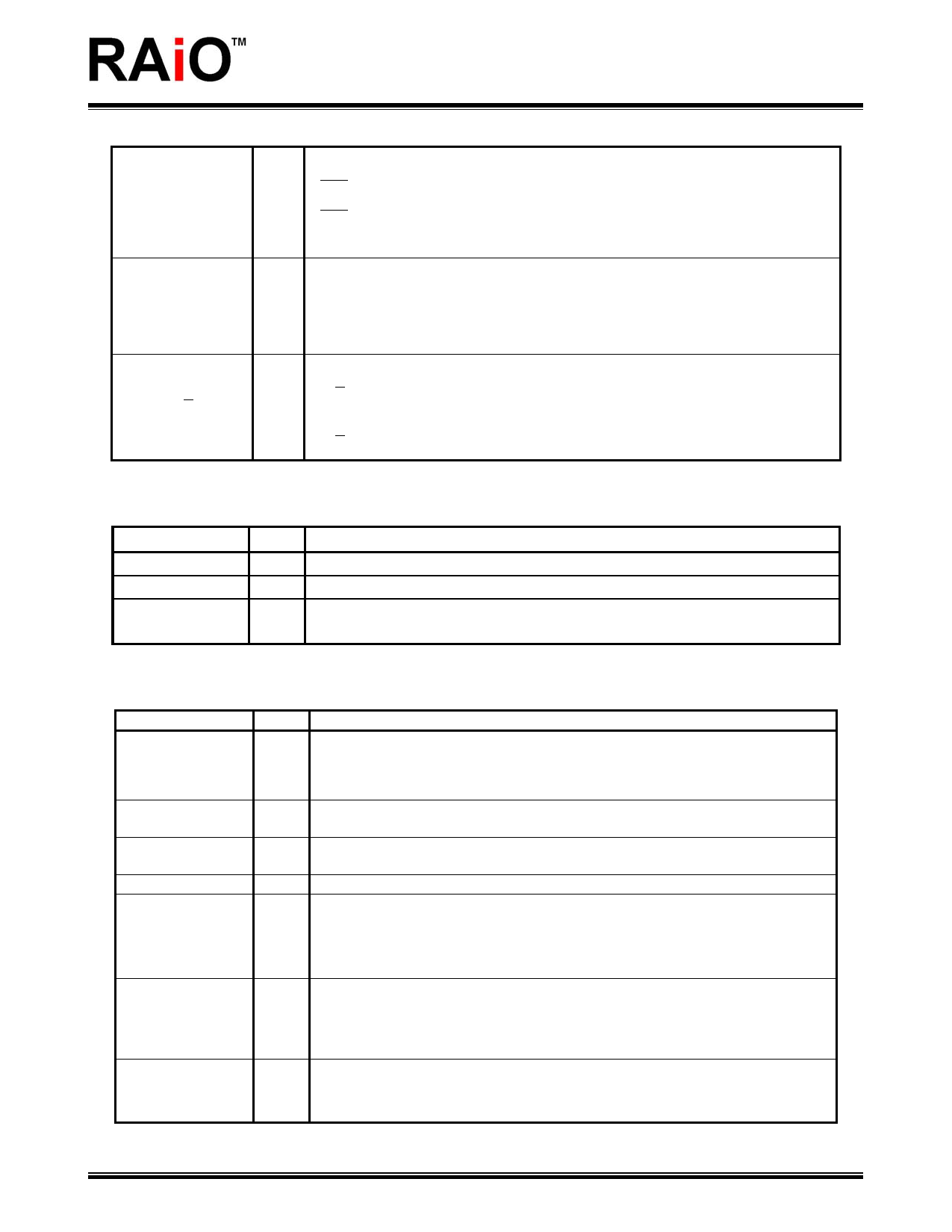

BIT4

P/ S

MPU Select

C86 = 0 The MPU interface is 8080 series.

I

C86 = 1 The MPU interface is 6800 series(Default).

Connect this pin to VDD for serial mode.

Data Bit Select

BIT4 = 0 The parallel mode is use 8-bit data bus.

I

BIT4 = 1 The parallel mode is use 4-bit data bus(Default).

Connect this pin to VDD for serial mode.

Parallel/Serial Select

I

P/ S = 0 The MPU interface is serial mode(Default). See the setting of

DB[7:6].

P/ S = 1 The MPU interface is parallel mode.

5-2 LCD Panel Interface

Pin Name

I/O

SEG0 ~ SEG127 O

COM0 ~ COM31 O

COMS_A[1:0]

O

COMS_B[1:0]

Description

Segment Signals for Panel

Common Signals for Panel

Icon Common Signals for Panel

5-.3 Clock and Power

Pin Name

I/O

V0~V4

O

C1P, C1M

I

C2P, C2M

I

VLCD

O

VREF

I

CLK_SEL

I

EXT_CLK

I

Description

Voltage Source of LCD Driver

The relationship of the power is VLCD>V0≧V1≧V2≧V3≧V4≧VSS。

These pins have to add external 0.1uF~1uF capacitor to GND.

Capacitor Input

These are used to connect a capacitor for internal Booster.

Capacitor Input

These are used to connect a capacitor for internal Booster.

Booster Output

Reference Voltage Input

This is the refeence voltage input when use an external regulator.

Normally keep this pin floating, if connect this signal to FPC then have to

add a 0.1uF capacitor to GND.

Clock Select

This pin is used to select the clock source. When CLK_SEL “1”, the clock

is generated by internal RC oscillator. When CLK_SEL is “0”, the system

clock is drive by external pin - EXT_CLK.

External Clock

When CLK_SEL is “0”, this pin is the external clock input. When

CLK_SEL is “1”, this pin do not used and has to connect VDD or GND.

RAiO TECHNOLOGY INC.

5/6

www.raio.com.tw