SST27SF010 查看數據表(PDF) - Silicon Storage Technology

零件编号

产品描述 (功能)

生产厂家

SST27SF010

SST27SF010 Datasheet PDF : 26 Pages

| |||

256 Kbit / 512 Kbit / 1 Mbit / 2 Mbit Multi-Purpose Flash

SST27SF256 / SST27SF512 / SST27SF010 / SST27SF020

Data Sheet

on VPP pin, VDD = 5V (±5%), VIL on CE# pin, and VIH on

OE# pin. The programming mode for SST27SF512 is acti-

vated by asserting 12V (±5%) on OE#/VPP pin, VDD = 5V

(±5%), and VIL on CE# pin. These devices are pro-

grammed byte-by-byte with the desired data at the desired

address using a single pulse (CE# pin low for

SST27SF256/512 and PGM# pin low for SST27SF010/

020) of 20 µs. Using the MTP programming algorithm, the

Byte-Programming process continues byte-by-byte until

the entire chip has been programmed.

Chip-Erase Operation

The only way to change a data from a “0” to “1” is by electri-

cal erase that changes every bit in the device to “1”. Unlike

traditional EPROMs, which use UV light to do the Chip-

Erase, the SST27SF256/512/010/020 uses an electrical

Chip-Erase operation. This saves a significant amount of

time (about 30 minutes for each Erase operation). The

entire chip can be erased in a single pulse of 100 ms (CE#

pin low for SST27SF256/512 and PGM# pin for

SST27SF010/020). In order to activate the Erase mode for

SST27SF256/010/020, the 12V (±5%) is applied to VPP

and A9 pins, VDD = 5V (±5%), VIL on CE# pin, and VIH on

OE# pin. In order to activate Erase mode for SST27SF512,

the 12V (±5%) is applied to OE#/VPP and A9 pins, VDD =

5V (±5%), and VIL on CE# pin. All other address and data

pins are “don’t care”. The falling edge of CE# (PGM# for

SST27SF010/020) will start the Chip-Erase operation.

Once the chip has been erased, all bytes must be verified

for FFH. Refer to Figures 13, 14, and 15 for the flowcharts.

Product Identification Mode

The Product Identification mode identifies the devices as

the SST27SF256, SST27SF512, SST27SF010 and

SST27SF020 and manufacturer as SST. This mode may

be accessed by the hardware method. To activate this

mode for SST27SF256/010/020, the programming equip-

ment must force VH (12V±5%) on address A9 with VPP pin

at VDD (5V±10%) or VSS. To activate this mode for

SST27SF512, the programming equipment must force VH

(12V±5%) on address A9 with OE#/VPP pin at VIL. Two

identifier bytes may then be sequenced from the device

outputs by toggling address line A0. For details, see Tables

3, 4, and 5 for hardware operation.

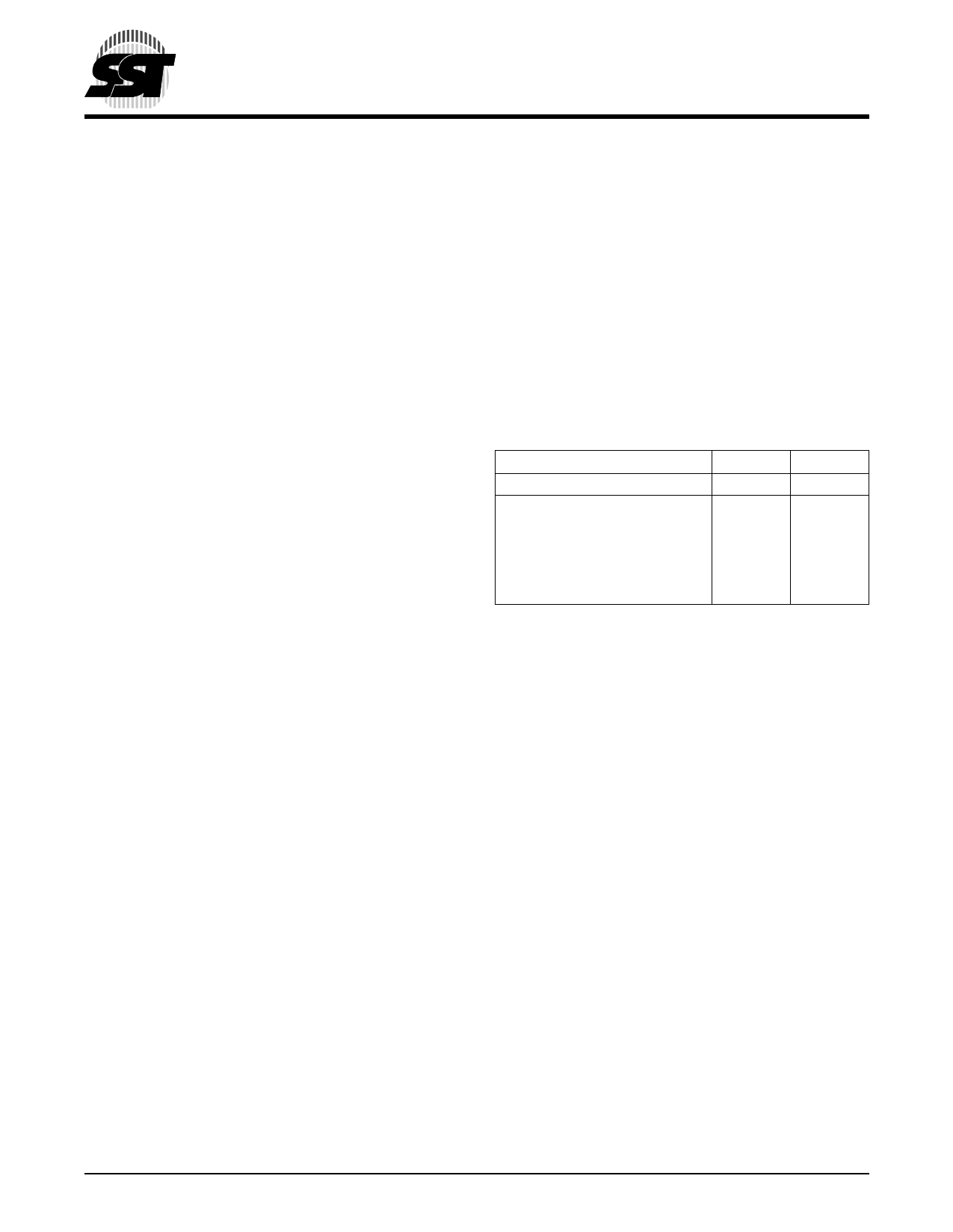

TABLE 1: PRODUCT IDENTIFICATION

Manufacturer’s ID

Device ID

SST27SF256

SST27SF512

SST27SF010

SST27SF020

Address

0000H

0001H

0001H

0001H

0001H

Data

BFH

A3H

A4H

A5H

A6H

T1.1 502

©2001 Silicon Storage Technology, Inc.

2

S71152-02-000 5/01 502