STK672-600 查看數據表(PDF) - SANYO -> Panasonic

零件编号

产品描述 (功能)

生产厂家

STK672-600 Datasheet PDF : 19 Pages

| |||

Usage Notes

STK672-600

1. STK672-600 and STK672-610 input signal functions and timing

(All inputs have no internal pull-up resistor and are TTL level Schmitt trigger inputs.)

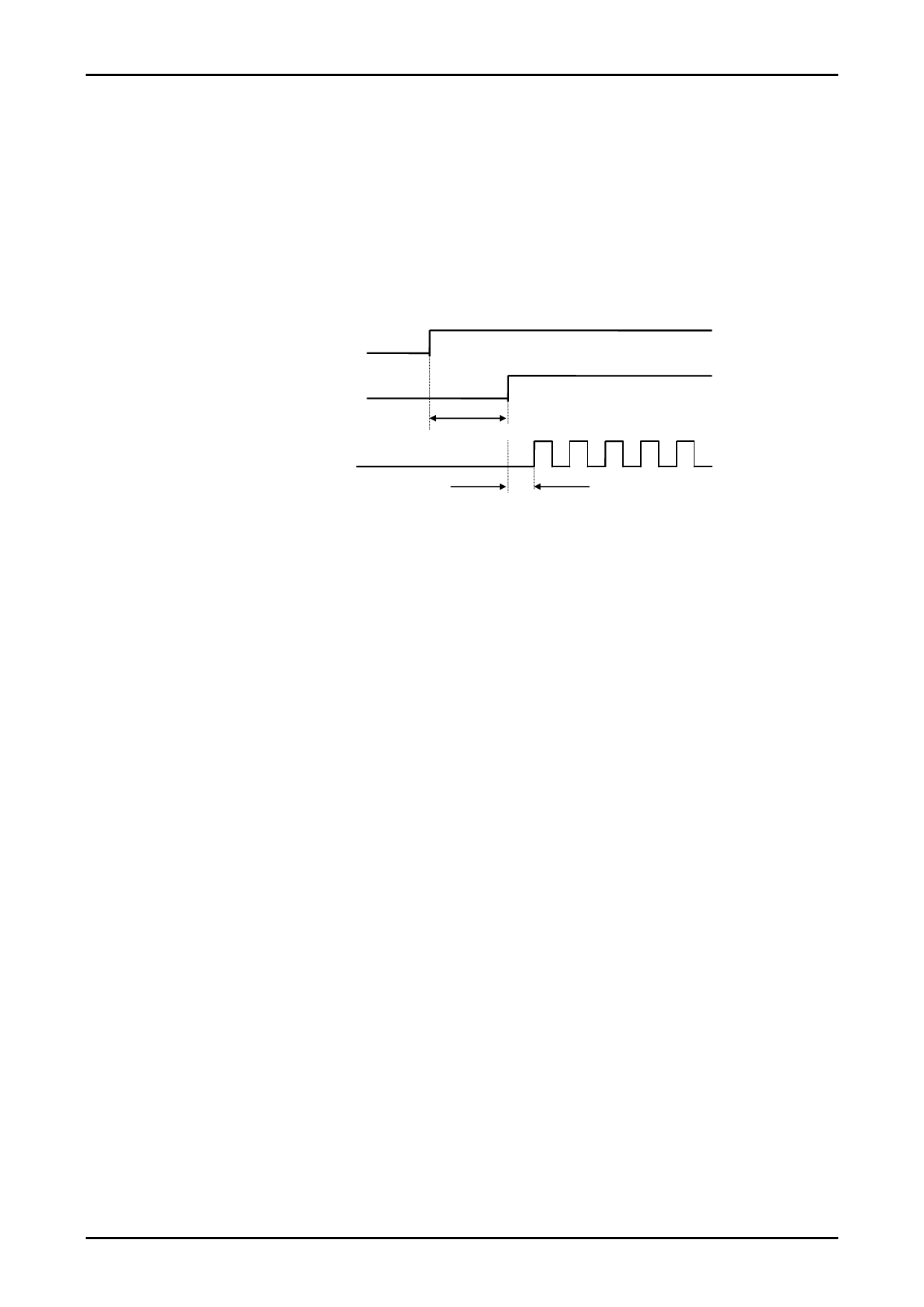

[RESETB and CLOCK (Input signal timing when power is first applied)]

As shown in the timing chart, a RESETB signal input is required by the driver to operate with the timing in which the

F1 gate is turned on first. The RESETB signal timing must be set up to have a width of at least 10μs, as shown below.

The capacitor CO2, and the resistors RO3 and RO4 in the application circuit form simple reset circuit that uses the

RC time constant rising time. However, when designing the RESETB input based on VIH levels, the application

must have the timing shown in figure.

Rise of the 5V supply

voltage

RESETB signal input

CLOCK signal

At least 10μs

At least 5μs

RESETB and CLOCK Signals Input Timing

[CLOCK (Phase switching clock)]

• Input frequency: DC to 50kHz

• Minimum pulse width: 10μs

• MODE2=1(High) Signals are read on the rising edge.

• MODE2=0(Low) Signals are read on the rising and falling edges.

[CWB (Motor direction setting)]

The direction of rotation is switched by setting CWB to 1 (high) or 0 (low). See the timing charts for details on the

operation of the outputs.

Note: The state of the CWB input must not be changed during the 6.25μs period before and after the rising edge of

the CLOCK input.

[ENABLE (Forcible on/off control of the A, AB, B, and BB outputs, and hybrid IC internal operation)]

ENABLE=1: Normal operation

ENABLE=0: Outputs A, AB, B, and BB forced to the off state.

If, during the state where CLOCK signal input is provided, the ENABLE pin is set to 0 and then is later

restored to the 1 state, the IC will resume operation with the excitation timing continued from before

the point ENABLE was set to 0.

If sudden stop is applied to the CLOCK signal used for motor rotation, the motor axis may advance beyond the

theoretical position due to inertia. To stop at the theoretical position, the SLOW DOWN setting for gradually slowing

the CLOCK cycle is required.

Enable must be initially set high for input as shown in the timing chart.

[MODE1 and MODE2 (Excitation mode selection)]

MODE1=0: 2-phase excitation

MODE2=1: Rising edge of CLOCK

MODE1=1: 1-2 phase excitation

MODE2=0: Rising and falling edges of CLOCK

See the timing charts for details on output operation in these modes.

Note: The state of the MODE input must not be changed during the 5μs period before and after the rising edge of the

CLOCK input.

No. A0755-11/19