FX602 查看數據表(PDF) - CML Microsystems Plc

零件编号

产品描述 (功能)

生产厂家

FX602 Datasheet PDF : 29 Pages

| |||

Calling Line Identifier

FX602

Packages

D4 / P3

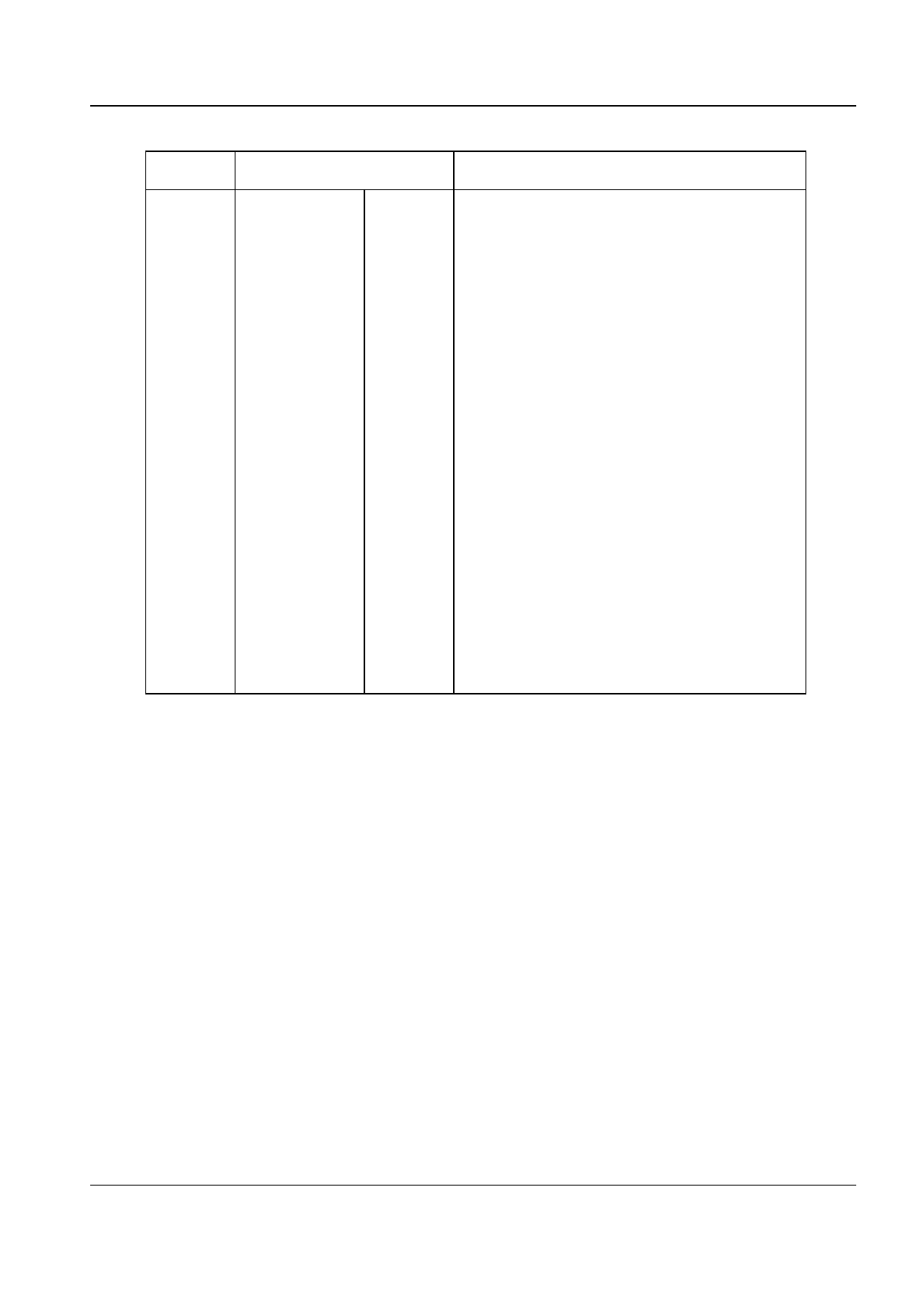

Signal

Description

Pin No.

12

Name

IRQN

13

DET

14

RXCK

15

RXD

16

VDD

Type

O/P

O/P

I/P

O/P

Power

An open-drain active low output that may be

used as an Interrupt Request / Wake-up input to

the associated µC. An external pull-up resistor

should be connected between this output and

VDD.

A logic level output driven by the Ring or Line

Polarity Reversal Detector, the Tone Alert

Detector or the FSK Level detect circuits,

depending on the operating mode. See section

1.5.1.

A logic level input which may be used to clock

received data bits out of the FSK Data Retiming

block.

A logic level output carrying either the raw output

of the FSK Demodulator or re-timed 8-bit

characters depending on the state of the RXCK

input. See section 1.5.6

The positive supply rail. Levels and thresholds

within the device are proportional to this voltage.

Should be decoupled to VSS by a capacitor

mounted close to the device pins.

Notes:

I/P = Input

I/P (S) = Schmitt trigger input

O/P = Output

BI = Bidirectional

© 1998 Consumer Microcircuits Limited

5

D/602/7