SY87700VZC وں¥çœ‹و•¸و“ڑè،¨ï¼ˆPDF) - Micrel

零ن»¶ç¼–هڈ·

ن؛§ه“پوڈڈè؟° (هٹں能)

ç”ںن؛§هژ‚ه®¶

SY87700VZC Datasheet PDF : 15 Pages

| |||

Micrel, Inc.

SY87700V

CHARACTERISTICS

Performance

The SY87700V PLL complies with the jitter specifications

proposed for SONET/SDH equipment defined by the Bellcore

Specifications: GR-253-CORE, Issue 2, December 1995 and

ITU-T Recommendations: G.958 document, when used with

differential inputs and outputs.

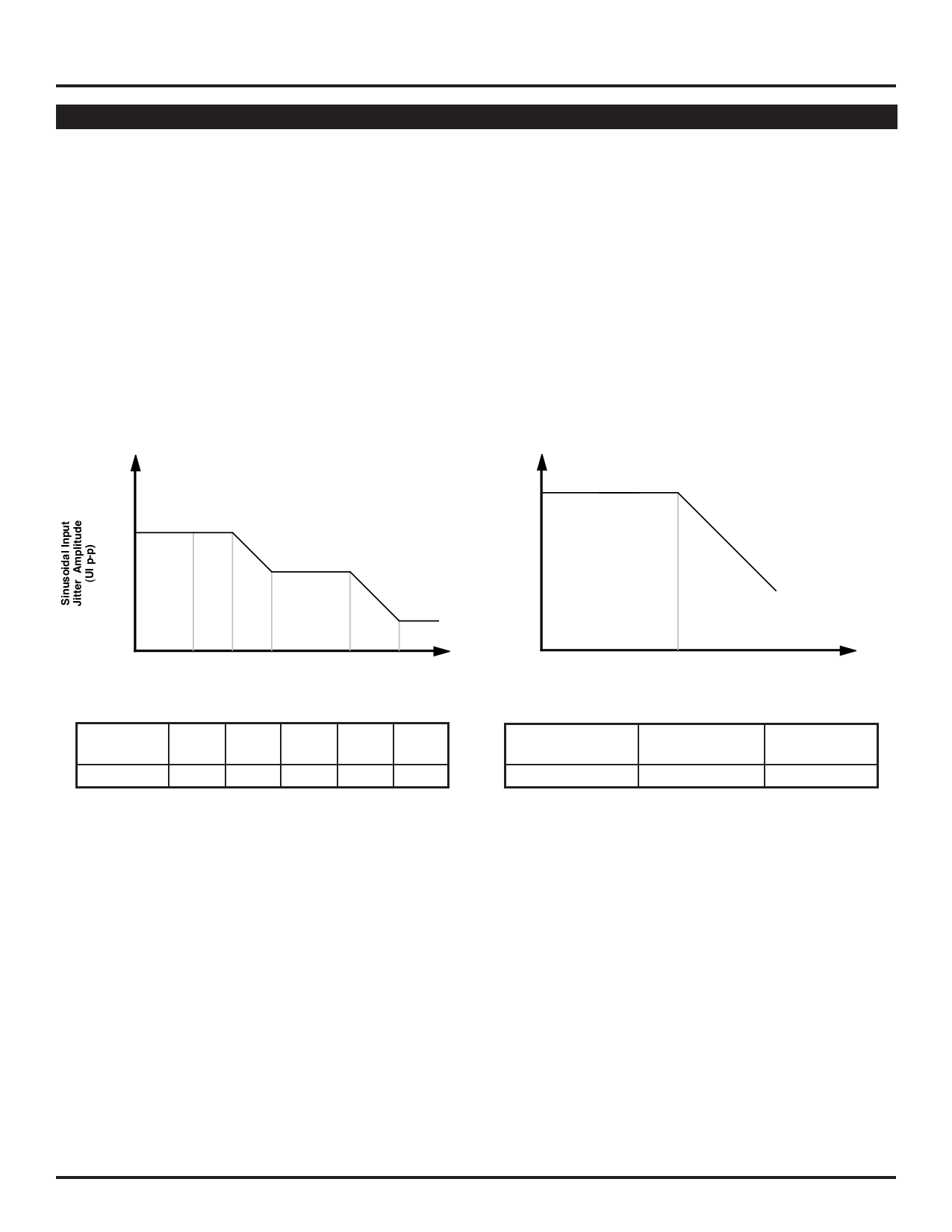

Input Jitter Tolerance

Input jitter tolerance is defined as the peak-to-peak

amplitude of sinusoidal jitter applied on the input signal that

causes an equivalent 1dB optical/electrical power penalty.

SONET input jitter tolerance requirement condition is the

input jitter amplitude which causes an equivalent of 1dB

power penalty.

Jitter Transfer

Jitter transfer function is defined as the ratio of jitter on

the output OC-N/STS-N signal to the jitter applied on the

input OC-N/STS-N signal versus frequency. Jitter transfer

requirements are shown in Figure 2.

Jitter Generation

The jitter of the serial clock and serial data outputs shall

not exceed .01 U.I. rms when a serial data input with no

jitter is presented to the serial data inputs.

A

15

-20dB/decade

1.5

-20dB/decade

0.40

f0 f1 f2

f4

ft

Frequency

OC/STS-N f0

f1

f2

f3

ft

Level

(Hz) (Hz) (Hz) (kHz) (kHz)

3

10

30

300

6.5

65

Figure 1. Input Jitter Tolerance

Jitter Transfer (dB)

0.1

-20

Acceptable

Range

-20dB/decade

fc

Frequency

OC/STS-N

Level

3

fc

(kHz)

130

P

(dB)

0.1

Figure 2. Jitter Transfer

M9999-111406

hbwhelp@micrel.com or (408) 955-1690

5