T83C5101 查看數據表(PDF) - Atmel Corporation

零件编号

产品描述 (功能)

生产厂家

T83C5101 Datasheet PDF : 58 Pages

| |||

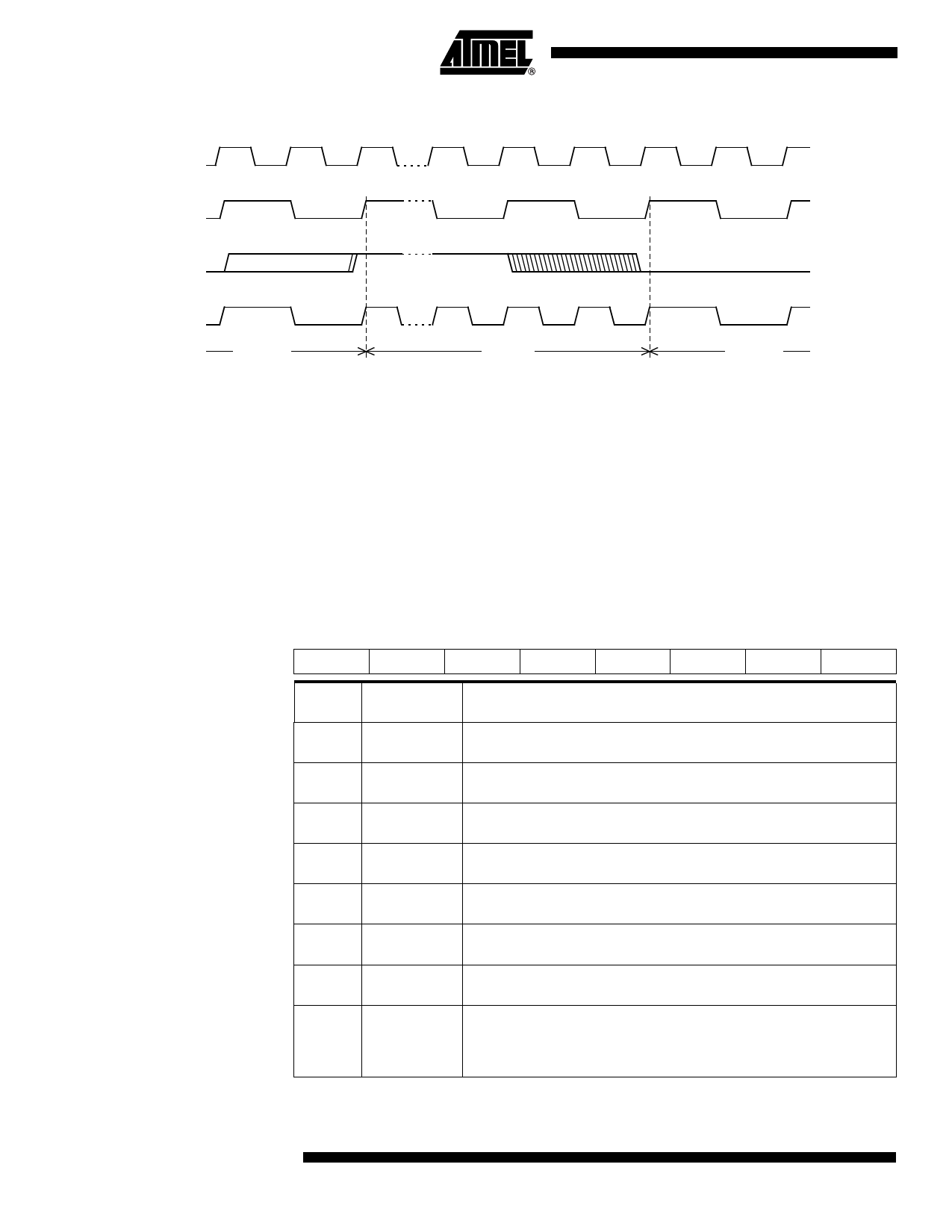

Figure 2. Mode Switching Waveforms

XTAL1

XTAL1:2

X2 bit

CPU clock

STD Mode

X2 Mode

STD Mode

The X2 bit in the CKCON register (See Table 2.) allows to switch from 12 clock cycles

per instruction to 6 clock cycles and vice versa. At reset, the standard speed is activated

(STD mode). Setting this bit activates the X2 feature (X2 mode).

CAUTION

In order to prevent any incorrect operation while operating in X2 mode, user must be

aware that all peripherals using clock frequency as time reference (UART, timers,

PCA...) will have their time reference divided by two. For example a free running timer

generating an interrupt every 20 ms will then generate an interrupt every 10 ms. UART

with 4800 baud rate will have 9600 baud rate.

Table 2. CKCON Register

CKCON - Clock Control Register (8Fh)

7

6

5

4

3

2

1

0

-

-

-

-

-

-

-

X2

Bit

Number

Bit

Mnemonic

Description

7

-

Reserved

The value read from this bit is indeterminate. Do not set this bit.

6

-

Reserved

The value read from this bit is indeterminate. Do not set this bit.

5

-

Reserved

The value read from this bit is indeterminate. Do not set this bit.

4

-

Reserved

The value read from this bit is indeterminate. Do not set this bit.

3

-

Reserved

The value read from this bit is indeterminate. Do not set this bit.

2

-

Reserved

The value read from this bit is indeterminate. Do not set this bit.

1

-

Reserved

The value read from this bit is indeterminate. Do not set this bit.

CPU and peripheral clock bit

0

X2

Clear to select 12 clock periods per machine cycle (STD mode,

FOSC=FXTAL/2).

Set to select 6 clock periods per machine cycle (X2 mode, FOSC=FXTAL).

Reset Value = XXXX XXX0b

Not bit addressable

9 T8xC5101/02

4233H–8051–02/08