M80C186 查看數據表(PDF) - Intel

零件编号

产品描述 (功能)

生产厂家

M80C186 Datasheet PDF : 59 Pages

| |||

M80C186

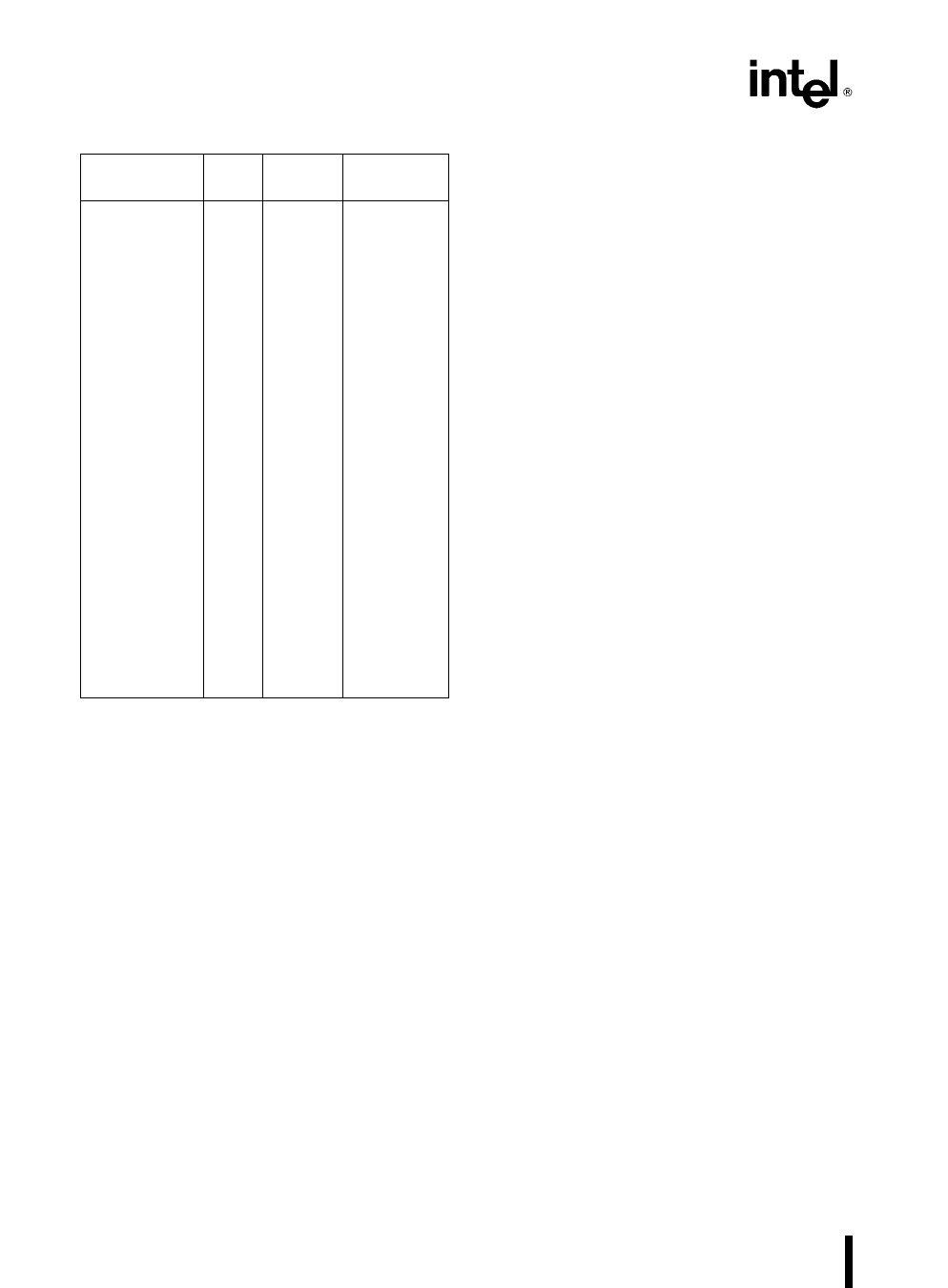

Table 4 M80C186 Interrupt Vectors

Interrupt

Name

Vector Default Related

Type Priority(4) Instructions

Divide Error

0

Exception

Single Step

1

Interrupt

NMI

2

Breakpoint

3

Interrupt

INT0 Detected

4

Overflow

Exception

Array Bounds

5

Exception

Unused-Opcode 6

Exception

ESC Opcode

7

Exception

Timer 0 Interrupt 8

Timer 1 Interrupt 18

Timer 2 Interrupt 19

Reserved

9

DMA 0 Interrupt 10

DMA 1 Interrupt 11

INT0 Interrupt

12

INT1 Interrupt

13

INT2 Interrupt

14

INT3 Interrupt

15

1(1) DIV IDIV

12(2) All

1 All

1(1) INT

1(1) INT0

1(1) BOUND

1(1)

1(1) (5)

Undefined

Opcodes

ESC Opcodes

2A(3)

2B(3)

2C(3)

3

4

5

6

7

8

9

NOTES

1 These are generated as the result of an instruction exe-

cution

2 This is handled as in the M8086

3 All three timers constitute one source of request to the

interrupt controller The Timer interrupts all have the same

default priority level with respect to all other interrupt

sources However they have a defined priority ordering

amongst themselves (Priority 2A is higher priority than 2B )

Each Timer interrupt has a separate vector type number

4 Default priorities for the interrupt sources are used only if

the user does not program each source into a unique prior-

ity level

5 An escape opcode will cause a trap if the M80C186 is in

compatible mode or if the processor is in enhanced mode

with the proper bit set in the peripheral control block relo-

cation register

BREAKPOINT INTERRUPT (TYPE 3)

A one-byte version of the INT instruction It uses 12

as an index into the service routine address table

(because it is a type 3 interrupt)

INT0 DETECTED OVERFLOW EXCEPTION

(TYPE4)

Generated during an INT0 instruction if the 0F bit is

set

16

ARRAY BOUNDS EXCEPTION (TYPE 5)

Generated during a BOUND instruction if the array

index is outside the array bounds The array bounds

are located in memory at a location indicated by one

of the instruction operands The other operand indi-

cates the value of the index to be checked

UNUSED OPCODE EXCEPTION (TYPE 6)

Generated if execution is attempted on undefined

opcodes

ESCAPE OPCODE EXCEPTION (TYPE 7)

Generated if execution is attempted of ESC opcodes

(D8H – DFH) In compatible mode operation ESC

opcodes will always generate this exception In en-

hanced mode operation the exception will be gener-

ated only if a bit in the relocation register is set The

return address of this exception will point to the ESC

instruction causing the exception If a segment over-

ride prefix preceded the ESC instruction the return

address will point to the segment override prefix

Hardware-generated interrupts are divided into two

groups maskable interrupts and non-maskable in-

terrupts The M80C186 provides maskable hardware

interrupt request pins INT0 – INT3 In addition mask-

able interrupts may be generated by the M80C186

integrated DMA controller and the integrated timer

unit The vector types for these interrupts is shown

in Table 4 Software enables these inputs by setting

the interrupt flag bit (IF) in the Status Word The in-

terrupt controller is discussed in the peripheral sec-

tion of this data sheet

Further maskable interrupts are disabled while serv-

icing an interrupt because the IF bit is reset as part

of the response to an interrupt or exception The

saved Status Word will reflect the enable status of

the processor prior to the interrupt The interrupt flag

will remain zero unless specifically set The interrupt

return instruction restores the Status Word thereby

restoring the original status of IF bit If the interrupt

return re-enables interrupts and another interrupt is

pending the M80C186 will immediately service the

highest-priority interrupt pending i e no instructions

of the main line program will be executed

Non-Maskable Interrupt Request (NMI)

A non-maskable interrupt (NMI) is also provided

This interrupt is serviced regardless of the state of

the IF bit A typical use of NMI would be to activate a

power failure routine The activation of this input

causes an interrupt with an internally supplied vector

value of 2 No external interrupt acknowledge se-

quence is performed The IF bit is cleared at the

beginning of an NMI interrupt to prevent maskable

interrupts from being serviced