LH540204 жҹҘзңӢж•ёж“ҡиЎЁпјҲPDFпјү - Sharp Electronics

йӣ¶д»¶зј–еҸ·

дә§е“ҒжҸҸиҝ° (еҠҹиғҪ)

з”ҹдә§еҺӮ家

LH540204 Datasheet PDF : 18 Pages

| |||

LH540204

OPERATIONAL MODES (contвҖҷd)

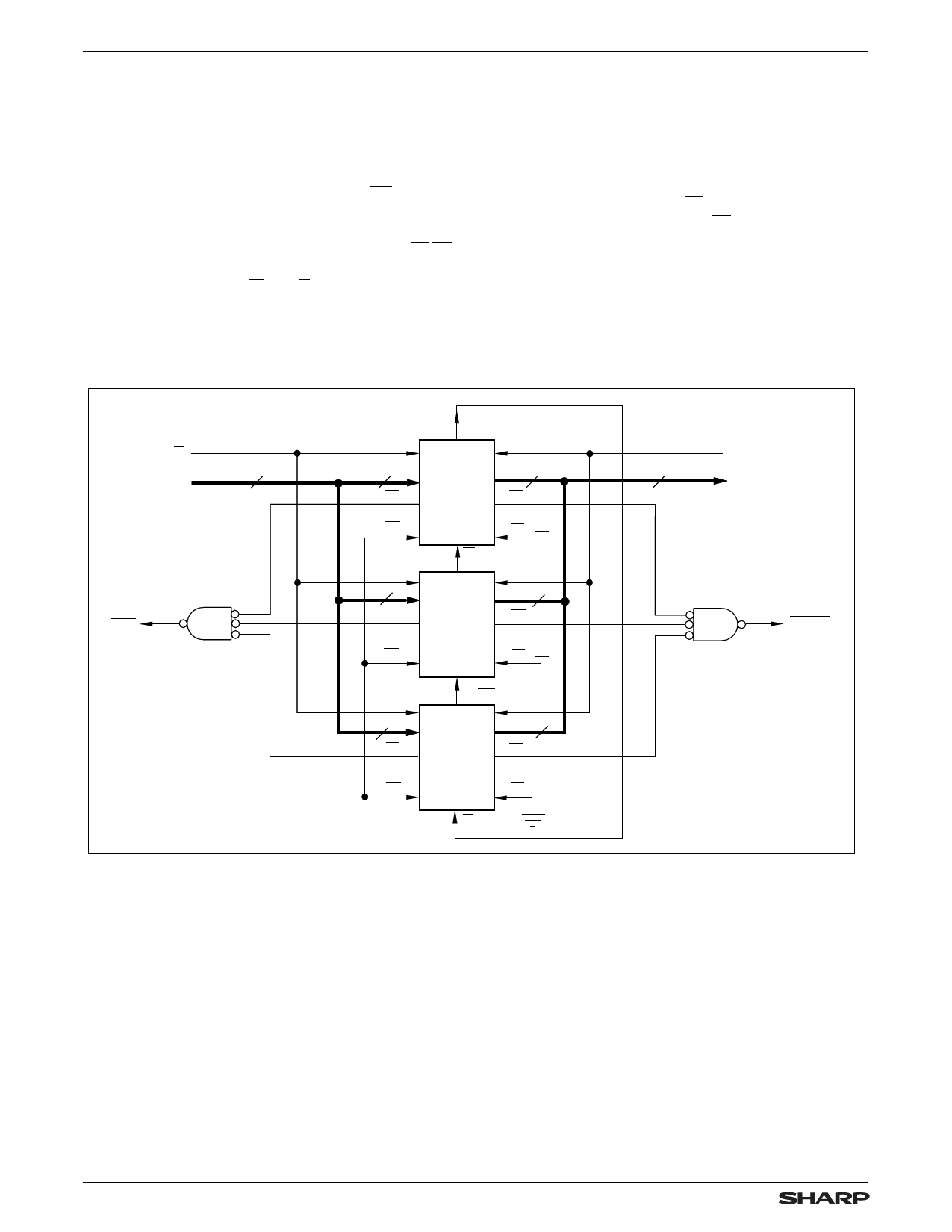

Depth Cascading

Depth cascading is implemented by configuring the

required number of LH540204s in depth-cascaded mode.

In this arrangement, the FIFOs are connected in a circular

fashion, with the Expansion Out output (XO) of each

device tied to the Expansion In input (XI) of the next

device. One FIFO in the cascade must be designated as

the вҖҳfirst-loadвҖҷ device, by tying its First Load input (FL/RT)

to ground. All other devices must have their FL/RT inputs

tied HIGH. In this mode, W and R signals are shared by

all devices, while logic within each LH540204 controls the

steering of data. Only one LH540204 is enabled during

any given write cycle; thus, the common Data In inputs of

CMOS 4096 Г— 9 Asynchronous FIFO

all devices are tied together. Likewise, only one

LH540204 is enabled during any given read cycle; thus,

the common Data Out outputs of all devices are wire-

ORed together.

In depth-cascaded mode, external logic should be

used to generate a composite Full Flag and a composite

Empty Flag, by ANDing the FF outputs of all LH540204

devices together and ANDing the EF outputs of all devices

together. Since FF and EF are assertive-LOW signals,

this вҖҳANDingвҖҷ actually is implemented using an assertive-

HIGH physical OR gate. The Half-Full Flag and the

Retransmit function are not available in depth-cas-

caded mode.

W

DATA IN

9

D0 - D8

FULL

RS

XO

9

9

9

LH540204

FF

EF

RS

FL Vcc

XI

XO

9

9

FF

LH540204 EF

RS

FL Vcc

9

FF

XI XO

LH540204

9

EF

RS

FL

XI

Figure 6. FIFO Depth Cascading (12288 Г— 9)

R

DATA OUT

Q0 - Q8

EMPTY

540204-19

6