GM71CS17800CLT-5 查看數據表(PDF) - Hynix Semiconductor

零件编号

产品描述 (功能)

生产厂家

GM71CS17800CLT-5 Datasheet PDF : 9 Pages

| |||

GM71C17800C

GM71CS17800CL

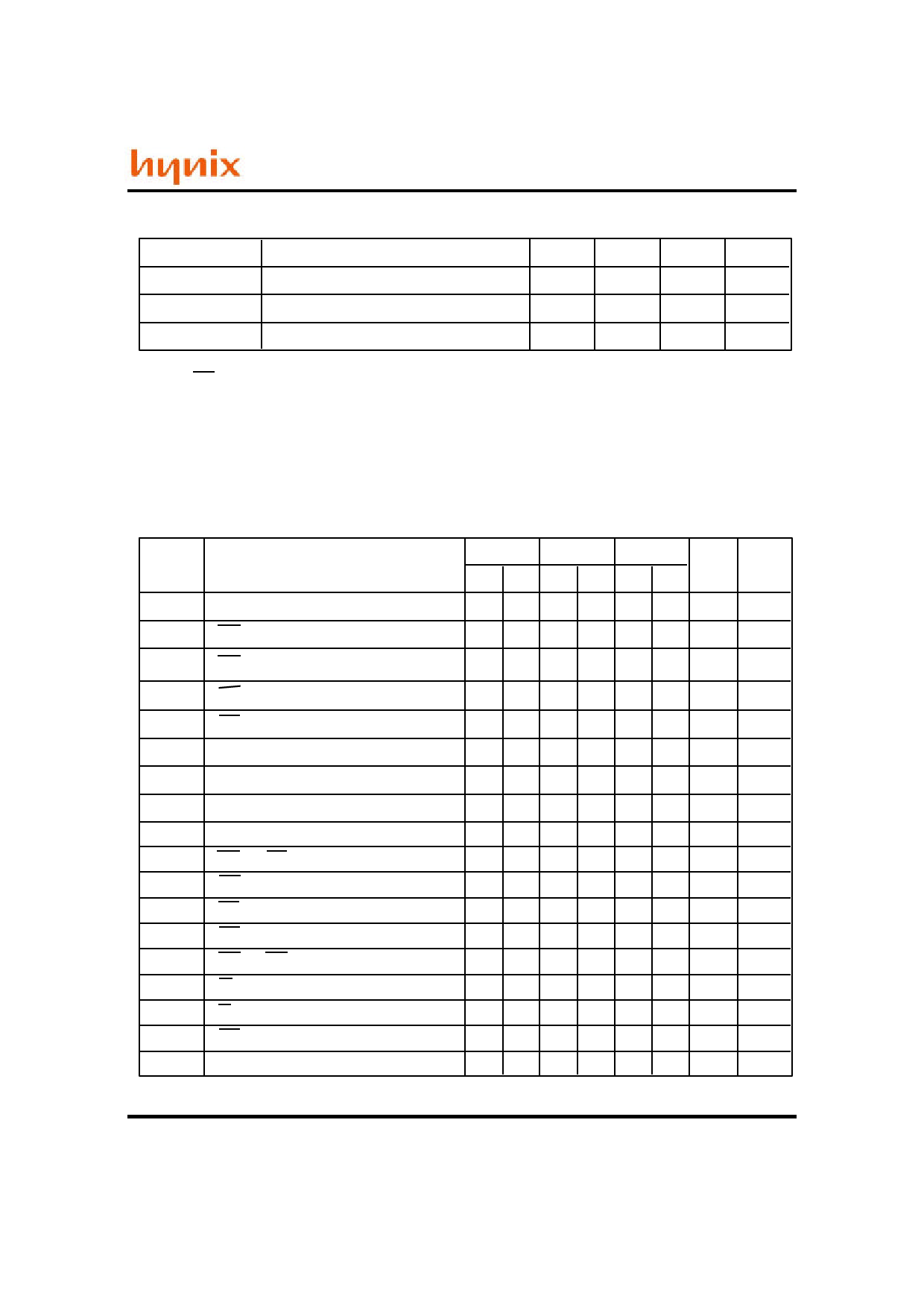

Capacitance (VCC = 5V+/-10%, TA = 25C)

Symbol

Parameter

Min Max Unit

CI1

Input Capacitance (Address)

-

5

pF

CI2

Input Capacitance (Clocks)

-

7

pF

CI/O

Output Capacitance (Data-In/Out)

-

7

pF

Note: 1. Capacitance measured with Boonton Meter or effective capacitance measuring method.

2. CAS = VIH to disable DOUT.

Note

1

1

1, 2

AC Characteristics (VCC = 5V+/-10%, TA = 0 ~ +70C, Vss = 0V, Note 1, 2, 18)

Test Conditions

Input rise and fall times : 5 ns

Output timing reference levels : 0.4V, 2.4V

Input timing reference levels : 0.8V, 2.4V

Output load : 2TTL gate + CL (100 pF)

(Including scope and jig)

Read, Write, Read-Modify-Write and Refresh Cycles (Common Parameters)

Symbol

Parameter

GM71C(S)17800 GM71C(S)17800 GM71C(S)17800

C/CL-5

C/CL-6

C/CL-7

Min Max Min Max Min Max

Unit

Note

tRC

Random Read or Write Cycle Time

90 - 110 - 130 - ns

tRP

RAS Precharge Time

30 - 40 - 50 - ns

tCP

CAS Precharge Time

7 - 10 - 10 - ns

tRAS RAS Pulse Width

tCAS CAS Pulse Width

tASR Row Address Set up Time

tRAH Row Address Hold Time

tASC Column Address Set-up Time

tCAH Column Address Hold Time

tRCD RAS to CAS Delay Time

tRAD RAS to Column Address Delay Time

tRSH

RAS Hold Time

tCSH

CAS Hold Time

tCRP CAS to RAS Precharge Time

tODD OE to DIN Delay Time

tDZO OE Delay Time from DIN

tDZC

CAS Delay Time from DIN

tT

Transition Time (Rise and Fall)

50 10,000 60 10,000 70 10,000 ns

13 10,000 15 10,000 18 10,000 ns

0-

0-

0 - ns

7 - 10 - 10 - ns

0-

0-

0 - ns

7 - 10 - 15 - ns

17 45 20 45 20 52 ns

3

12 30 15 30 15 35 ns

4

13 - 15 - 18 - ns

50 - 60 - 70 - ns

5-

5-

5 - ns

13 - 15 - 18 - ns

5

0-

0-

0 - ns

6

0-

0-

0 - ns

6

3 50 3 50 3 50 ns

7

Rev 0.1 / Apr’01