UPD75048CW 查看數據表(PDF) - NEC => Renesas Technology

零件编号

产品描述 (功能)

生产厂家

UPD75048CW Datasheet PDF : 68 Pages

| |||

µPD75048

6.5 WATCH TIMER

The µPD75048 has a built-in 1-ch watch timer. The clock timer has the following functions.

• Sets the test flag (IRQW) with 0.5sec interval.

The standby mode can be released by IRQW.

• 0.5 second interval can be generated either from the main system clock or subsystem clock.

• Time interval can be advanced to 128 times faster (3.91 ms) by setting the fast mode. This is

convenient for program debugging, test, etc.

• Arbitrary frequency (2.048kHz/4.096kHz/32.768kHz) can be output to the P23/BUZ pin. This can be

used for beep and system clock frequency trimming.

• The frequency divider circuit can be cleared so that zero second clock start is possible.

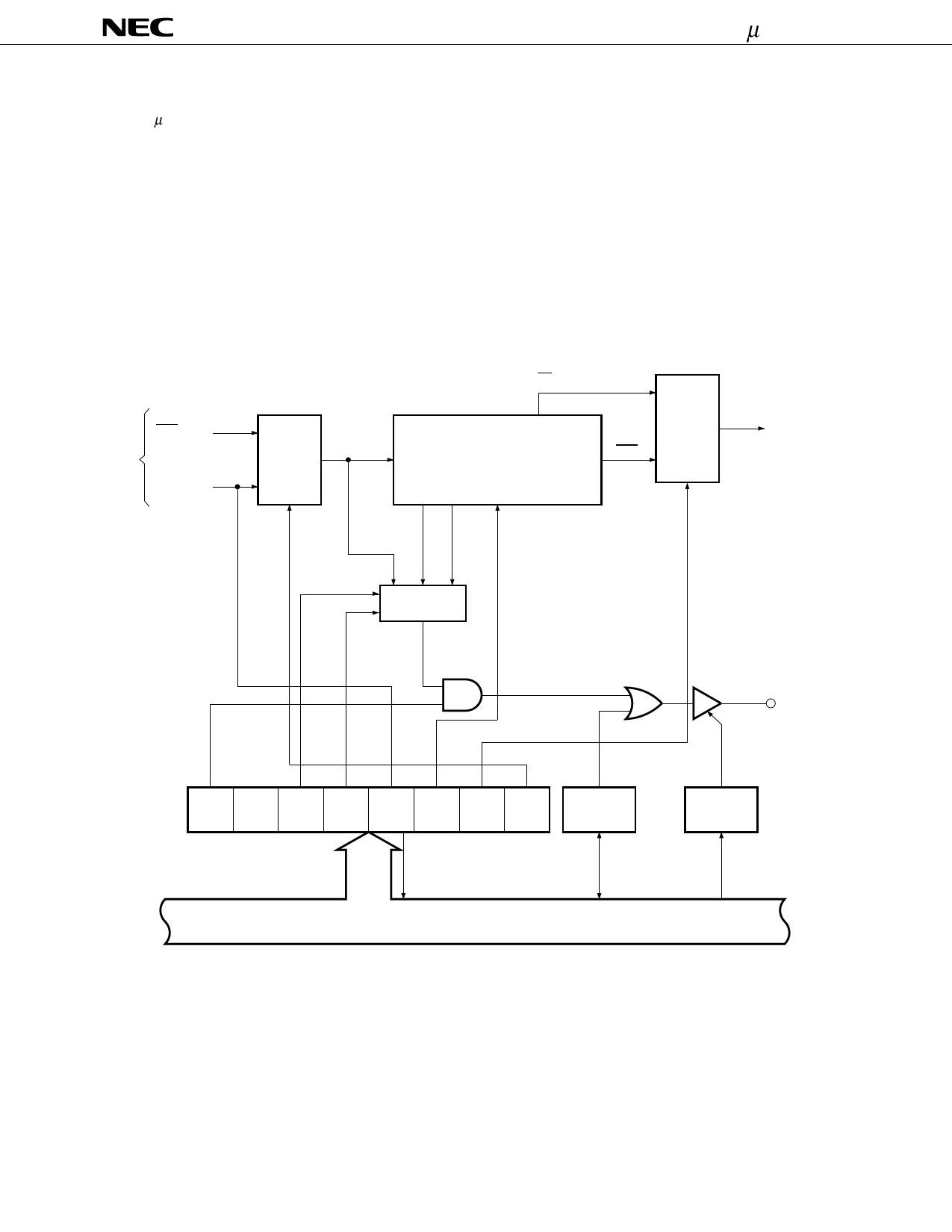

fW

27

(256

Hz:3.91

ms)

From the

clock

generator

fX

128

(32.768 kHz)

fXT

(32.768 kHz)

fW

(32.768 kHz)

Selector

Frequency divider

4 kHz 2 kHz

Clear

Selector

fw

214

( ) 2 Hz

0.5 sec

INTW

( ) IRQW

set signal

Selector

Output buffer

P23/BUZ

WM

WM7 0 WM5 WM4 WM3 WM2 WM1 WM0

8

Bit test

instruction

Internal bus

PORT2.3

P23

output

latch

Bit 2 of PMGB

Port 2

input/output

mode

( ) is for fX = 4.194304 MHz, fXT = 32.768 KHz.

Fig. 6-4 Clock Timer Block Diagram

26