V386GLF 查看數據表(PDF) - Integrated Circuit Systems

零件编号

产品描述 (功能)

生产厂家

V386GLF Datasheet PDF : 10 Pages

| |||

V386

8-BIT LVDS RECEIVER FOR VIDEO

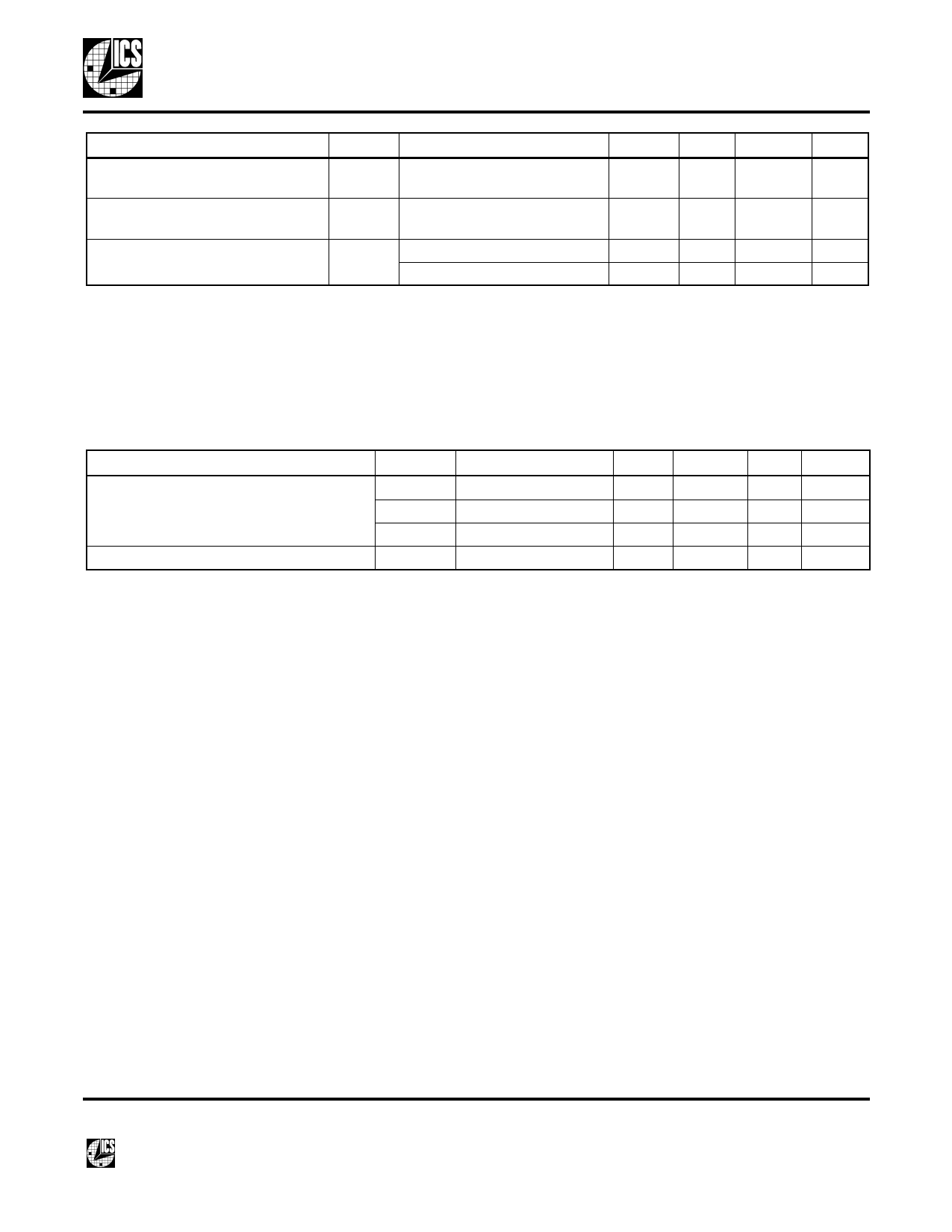

Parameter

Symbol

Conditions

Min. Typ. Max. Units

Receiver Input Strobe Position for

Bit5

RSPos5 f = 85 MHz, T = 11.76 ns

8.89 9.24

9.59

ns

Receiver Input Strobe Position for

Bit6

RSPos6 f = 85 MHz, T = 11.76 ns

10.57 10.92 11.27

ns

RxIn Skew Margin (see note and

Rskm f = 85 MHz, T = 11.76 ns

300

ps

Figure 8)

f = 65 MHz, T = 15.38 ns

500

ps

Note: The skew margins mean the maximum timing tolerance between the clock and data channel when the

receiver still works well. This margin takes into acount the receiver input setup and hold time, and internal clock

jitter (i.e., internal data sampling window - RSPos). Thyis margin allows for LVDS transmitter pulse position,

interconnect skew, inter-symbol interference and intrinsic channel mismatch which will cause the skew between

clock (RC+ and RCK-) and data (RX[n]+ and RX[n]- ; n =0, 1, 2, 3) channels.

Thermal Characteristics

Parameter

Thermal Resistance Junction to Ambient

Thermal Resistance Junction to Case

Symbol

θJA

θJA

θJA

θJC

Conditions

Still air

1 m/s air flow

3 m/s air flow

Min.

Typ.

84

76

67

50

Max.

Units

°C/W

°C/W

°C/W

°C/W

V386 Datasheet

6

5/25/05

Revision 2.0

Integrated Circuit Systems • 525 Race Street, San Jose, CA 95126 • tel (408) 297-1201 • www.icst.com