V826516K04SXTG-B0 查看數據表(PDF) - Mosel Vitelic Corporation

零件编号

产品描述 (功能)

生产厂家

V826516K04SXTG-B0

V826516K04SXTG-B0 Datasheet PDF : 13 Pages

| |||

MOSEL VITELIC

V826516K04S

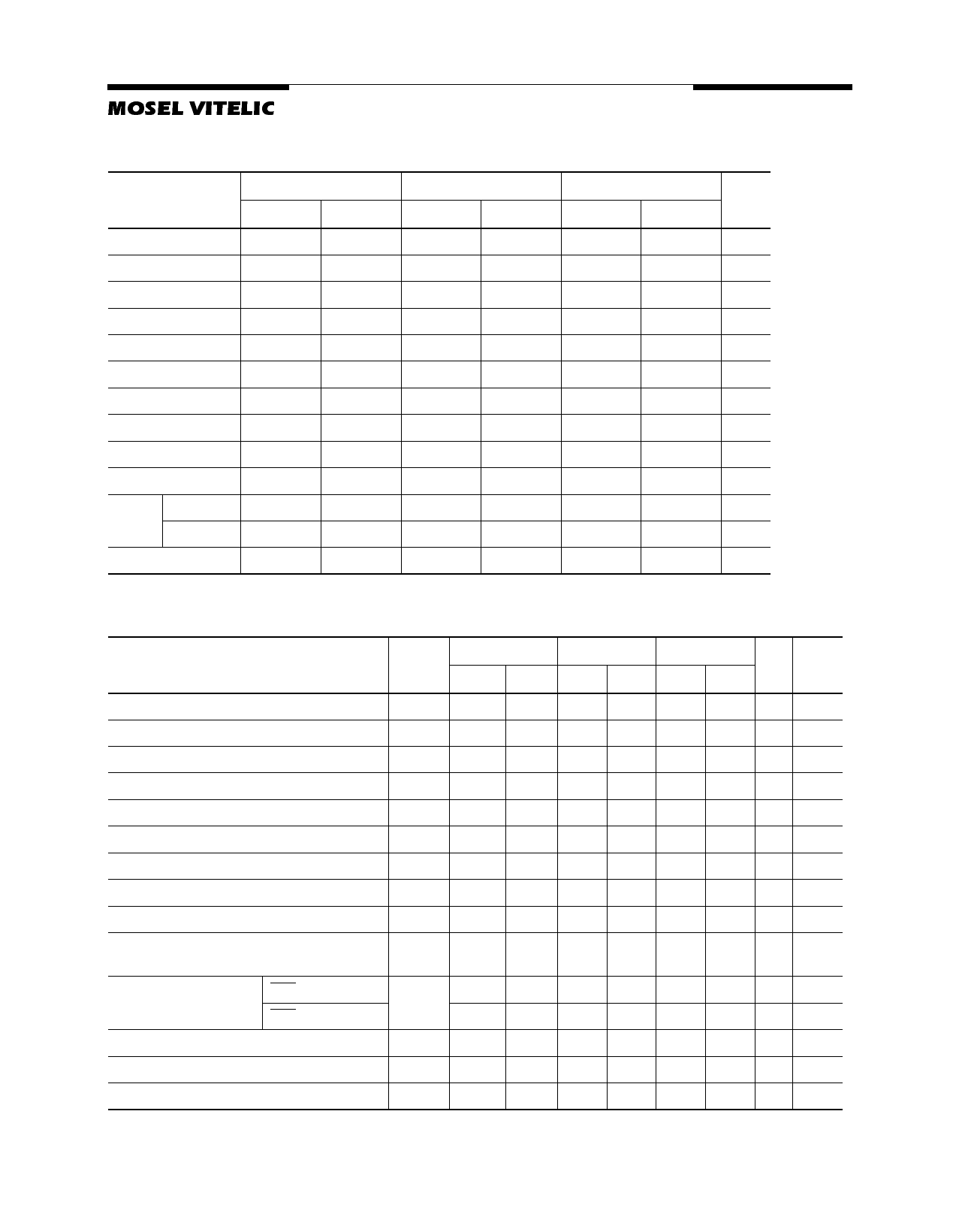

DDR SDRAM Module IDD Spec Table

B1(DDR266@CL=2) B0(DDR266@CL=2.5)

Symbol

typical

worst

typical

worst

IDD0

720

760

720

760

IDD1

1120

1200

1120

1200

IDD2P

168

200

168

200

IDD2F

320

360

320

360

IDD2Q

240

280

240

280

IDD3P

200

240

200

240

IDD3N

320

360

320

360

IDD4R

1200

1320

1200

1320

IDD4W

1080

1200

1080

1200

IDD5

1560

1640

1560

1640

IDD6 Normal

16

16

16

16

Low power

8

8

8

8

IDD7

2080

2240

2080

2240

A1(DDR200@CL=2)

typical

worst

640

680

1000

1080

152

184

280

320

216

256

160

200

240

280

1000

1120

840

960

1140

1520

16

16

8

8

2000

2200

Unit

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

AC Characteristics (AC operating conditions unless otherwise noted)

(PC266A)

Parameter

Symbol Min Max

Row Cycle Time

Auto Refresh Row Cycle Time

Row Active Time

Row Address to Column Address Delay

Row Active to Row Active Delay

Column Address to Column Address Delay

Row Precharge Time

Write Recovery Time

Last Data-In to Read Command

Auto Precharge Write Recovery + Precharge

Time

tRC

tRFC

tRAS

tRCD

tRRD

tCCD

tRP

tWR

tDRL

tDAL

60

-

67

-

45

120K

18

-

14

-

1

-

18

-

15

-

1

-

35

-

System Clock Cycle Time CAS Latency = 2.5

tCK

CAS Latency = 2

7

12

7.5

12

Clock High Level Width

Clock Low Level Width

Data-Out edge to Clock edge Skew

tCH

0.45 0.55

tCL

0.45 0.55

tAC

-0.75 0.75

(PC266B)

Min Max

65

-

75

-

48 120K

20

-

15

-

1

-

20

-

15

-

1

-

35

-

7.5

12

10

12

0.45 0.55

0.45 0.55

-0.75 0.75

(PC200)

Min Max Unit Note

70

-

ns

80

-

ns

50 120K ns

20

-

ns

15

-

ns

1

- CLK

20

-

ns

15

-

ns

1

- CLK

35

-

ns

8

12 ns

10

12 ns

0.45 0.55 CLK

0.45 0.55 CLK

-0.8 0.8 ns

V826516K04S Rev. 1.1 March 2002

8