VSC7125 查看數據表(PDF) - Vitesse Semiconductor

零件编号

产品描述 (功能)

生产厂家

VSC7125 Datasheet PDF : 16 Pages

| |||

Data Sheet

VSC7125

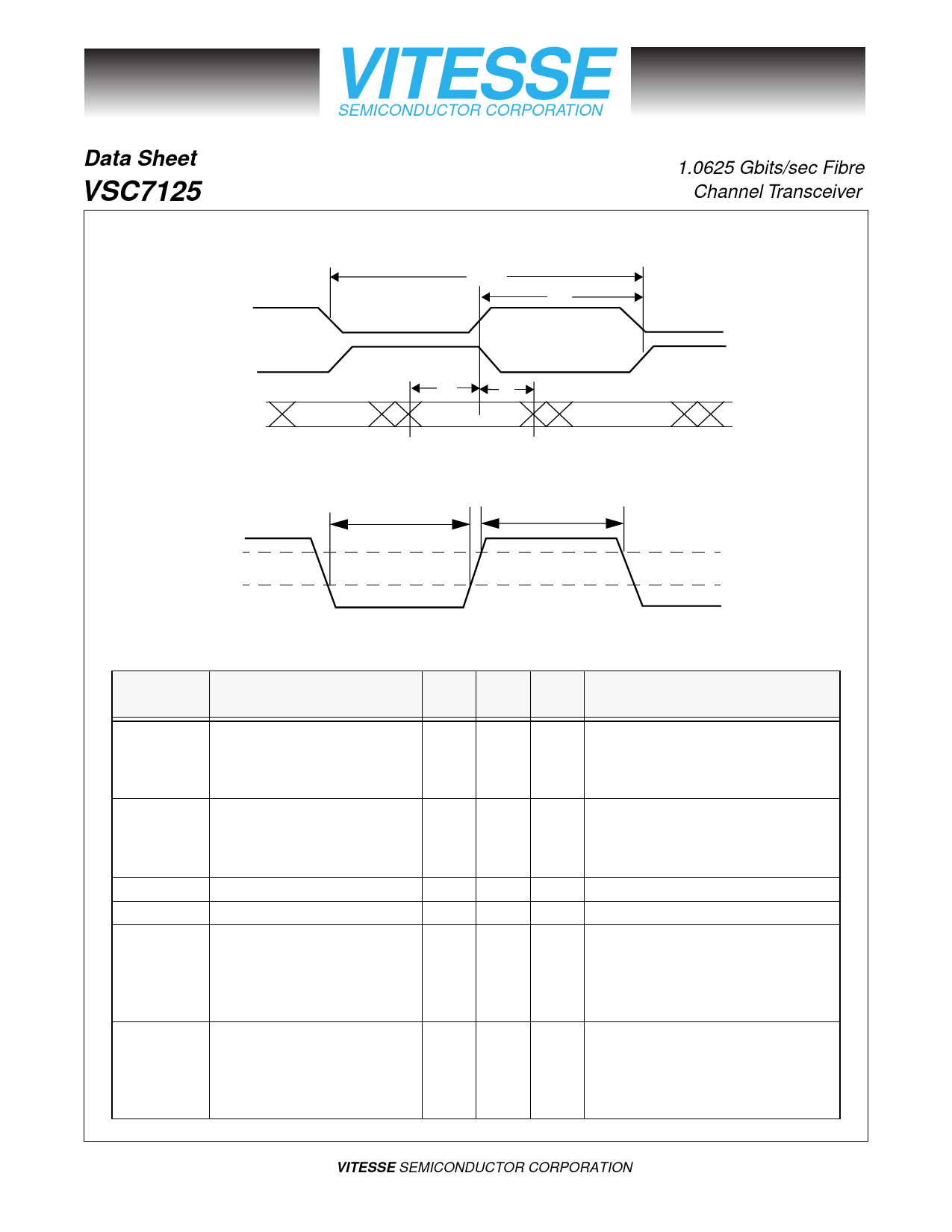

RCLK

RCLKN

R0:9

VITESSE

SEMICONDUCTOR CORPORATION

Figure 5: Receive Timing Waveforms

T4

T3

1.0625 Gbits/sec Fibre

Channel Transceiver

Data Valid

T1

T2

Data Valid

Data Valid

REFCLK

Figure 6: REFCLK Timing Waveforms

TL

TH

Vih(min)

Vil(max)

Table 3: Reference Clock Requirements

Parameters

Description

FR

Frequency Range

Min

Max

Unit

s

Conditions

Range over which both transmit and

receive reference clocks on any link

100 110 MHz may be centered

FO

Frequency Offset

Maximum frequency offset between

transmit and receive reference clocks

-200 200 ppm. on one link

DC

TRCR,TRCF

REFCLK

Jitter

REFCLK

Jitter

REFCLK duty cycle

REFCLK rise and fall time

REFCLK Jitter Power

5MHz

∫ PhaseNoise

100 H z

REFCLK Jitter Power

5MHz

∫ PhaseNoise

100 H z

30

70

% Measured at 1.5V

—

2.0

ns. Between Vil(max) and Vih(min)

dbc, RMS for FC compliant output

—

2

ps. data jitter

dbc, RMS for 10-12 Bit Error Ratio

—

40

ps. with zero length external path. Tested

on a sample basis

G52121-0, Rev. 4.1

4/23/98

© VITESSE SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

Page 7