VSC870TX 查看數據表(PDF) - Vitesse Semiconductor

零件编号

产品描述 (功能)

生产厂家

VSC870TX Datasheet PDF : 40 Pages

| |||

Data Sheet

VSC870

VITESSE

SEMICONDUCTOR CORPORATION

High Performance Serial

Backplane Transceiver

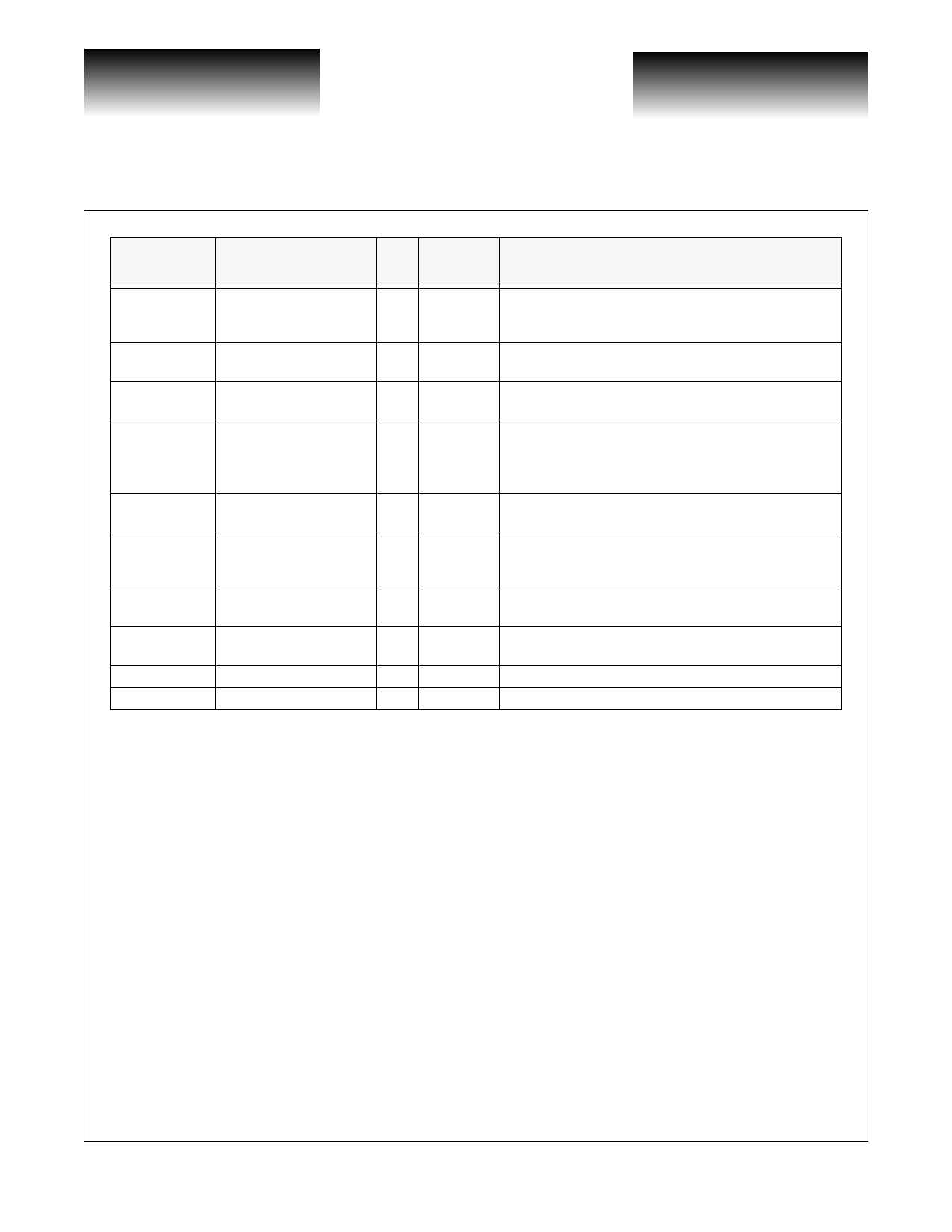

Symbol

DLYEN/

CCKIN

FACLPBK

WCLK

REFCLK

RESET

TESTEN

LTIME

VSCTE

VDDA

VSSA

Name

I/O

Freq

Type

Description

Delay Enable/Cell Clock

Input

I

<1MHz

TTL

If BYPASS is LOW, this signal can be set HIGH to enable

REN delay mode. In Cell Mode, DLYEN/CCKIN can be

used as an input for cell clock alignment.

Facility Loopback

I

<1MHz

TTL

When this signal is HIGH, the serial input is looped back

to the serial output. It should be normally set LOW.

Word Clock

O

62.5MHz

TTL

The word clock is a delayed version of the WSIN signal.

Local Reference Clock

A 62.5 MHz local reference clock that is used to keep the

I

62.5MHz CRU close to the incoming bit clock frequency before the

TTL alignment process begins. Is also used as a reference

clock for the CMU.

Reset

I

<1MHz

TTL

Global chip reset (active HIGH).

Scan Test Enable

I

<1MHz

TTL

When TESTEN is HIGH, the REFCLK is used in place

of the bit clock for low speed testing. Used for ATE

testing only. Set to logic LOW during normal operation.

Loop Time Mode

I

62.5Mb/s LTIME is set HIGH to use the recovered bit clock for the

TTL transmit side.

NOR Chain Test Enable I

<1MHz

TTL

Used for ATE testing of the parametric NOR chain in the

I/O frame. Set to logic LOW during normal operation.

CMU Power Supply

P

3.3V Clean power supply for CMU

CMU Ground

P

0V

Clean ground for CMU

G52190-0, Rev 4.1

01/05/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Page 5