VSC8111QB1 查看數據表(PDF) - Vitesse Semiconductor

零件编号

产品描述 (功能)

生产厂家

VSC8111QB1

VSC8111QB1 Datasheet PDF : 26 Pages

| |||

Data Sheet

VSC8111

VITESSE

SEMICONDUCTOR CORPORATION

ATM/SONET/SDH 155/622 Mb/s Transceiver

Mux/Demux with Integrated Clock Generation

lel to serial conversion of the low speed data (TXIN [7:0]) is selected and converted back to parallel data in the

receiver section and presented at the low speed parallel outputs (RXOUT [7:0]). See Figure 4. The internally

generated 155MHz/622MHz clock is used to generate the low speed receive clock output (RXLSCKOUT). In

Equipment Loopback mode the transmit data (TXIN [7:0]) is serialized and presented at the high speed output

(TXDATAOUT) along with the high speed transmit clock (TXCLKOUT) which is generated by the on board

clock multiplier unit.

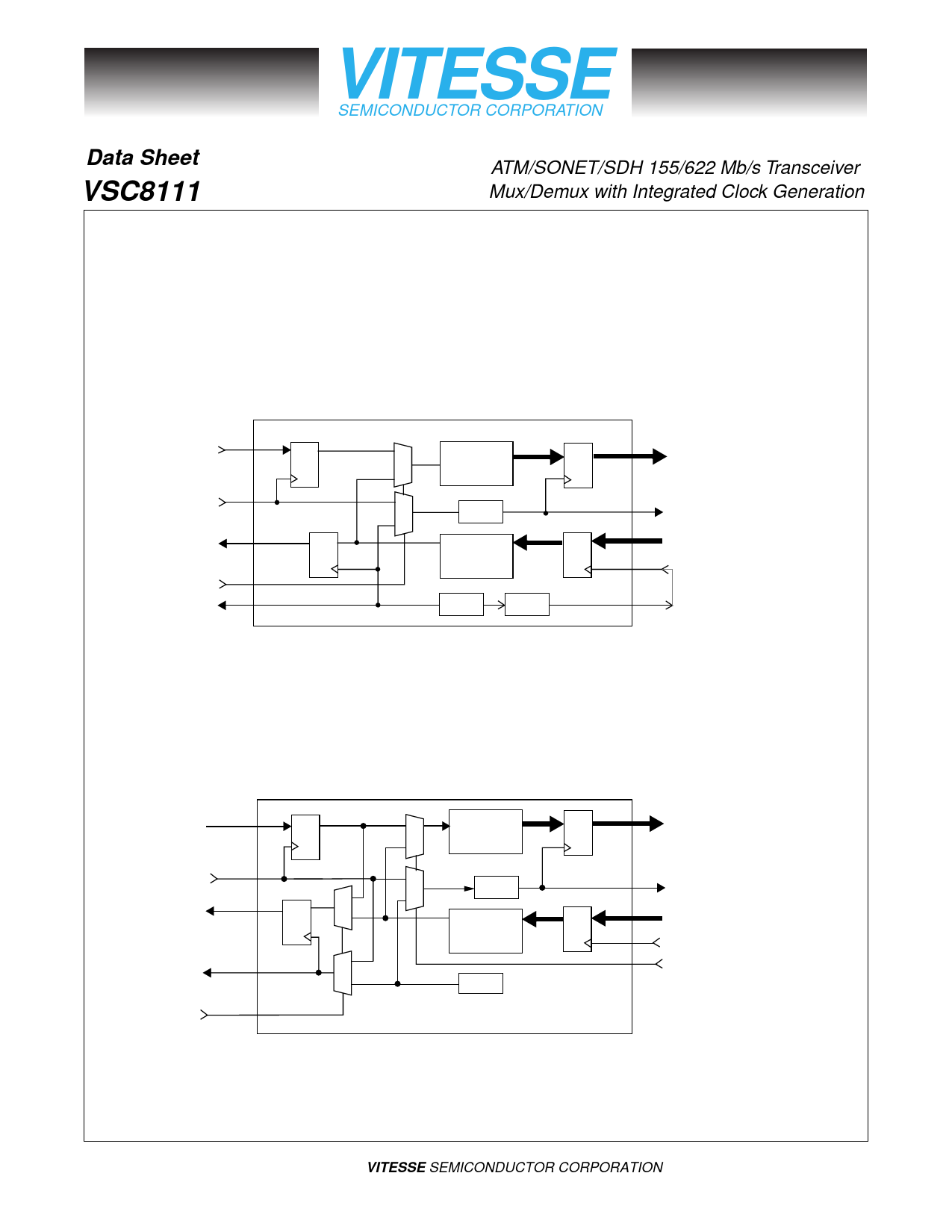

Figure 4: Equipment Loopback Data Path

RXDATAIN

RXCLKIN

TXDATAOUT

EQULOOP

TXCLKOUT

DQ

QD

0

1:8

Serial to

1

Parallel

0

÷8

1

8:1

Parallel to

Serial

DQ

QD

PLL

÷8

RXOUT[7:0]

RXLSCKOUT

TXIN[7:0]

TXLSCKIN

TXLSCKOUT

Split Loopback

Equipment and facility loopback modes can be enabled simultaneously. See descriptions for equipment and

facility loop modes above. The only change is, since they are both active, RXDATAIN will not be deserialized

and presented to RXOUT[0:7] and TXIN[0:7] will not be serialized and present to TXDATAOUT.

Figure 5: Split Loopback Datapath

RXDATAIN

RXCLKIN

TXDATAOUT

TXCLKOUT

FACLOOP

DQ

1

QD

0

1

0

0

1:8

Serial to

Parallel

1

0

÷8

1

8:1

Parallel to

Serial

PLL

DQ

QD

RXOUT[7:0]

RXLSCKOUT

TXIN[[7:0]

TXLSCLKIN

EQULOOP

G52142-0, Rev 4.2

8/31/98

© VITESSE SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

Page 5