VSC8140QR 查看數據表(PDF) - Vitesse Semiconductor

零件编号

产品描述 (功能)

生产厂家

VSC8140QR

VSC8140QR Datasheet PDF : 34 Pages

| |||

VITESSE

SEMICONDUCTOR CORPORATION

2.48832Gb/s 16:1 SONET/SDH

Transceiver with Integrated Clock Generator

Data Sheet

VSC8140

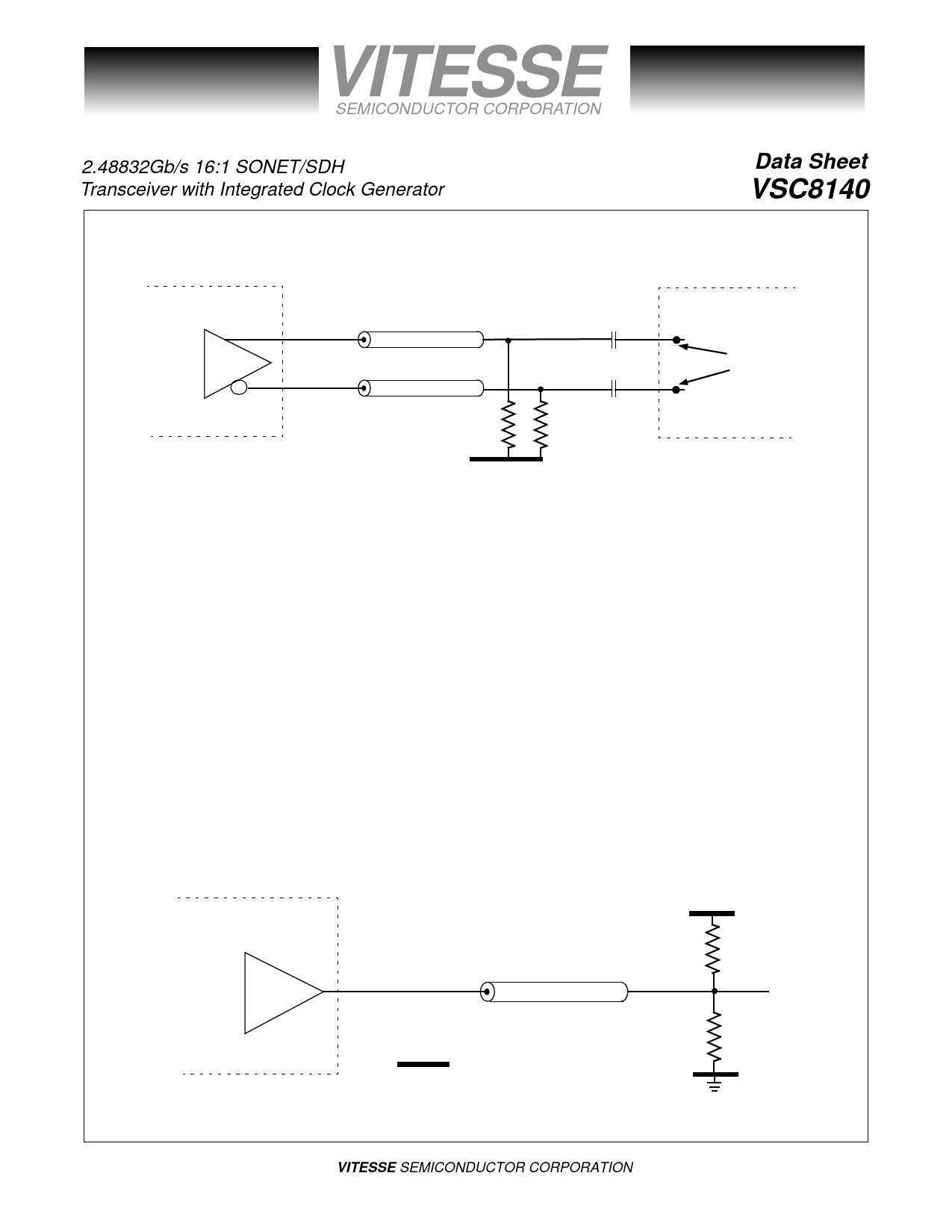

Figure 5: AC Termination of Low-Speed LVPECL RXCLK16O, RXCLK16_32O, TXCLK16O Outputs

VSC8140

Zo

Zo

50Ω

100nF

50Ω 100nF

VCC-2V

downstream

bias point

generated

internally

Receiver Low-Speed Interface

The demultiplexed serial stream is made available by a 16-bit single-ended LVPECL interface

RXOUT[15:0] with accompanying differential LVPECL divide-by-16 clock RXCLK16O± and selectable

LVPECL divide-by-16 or -32 clock RXCLK16_32O±.

RXCLKO_FREQSEL is used to select RXCLK16_32O±. RXCLKO_FREQSEL = “0” designates

RXCLK16_32O± output as 77.76MHz, RXCLKO_FREQSEL = “1” designates RXCLK16_32O± output as

155.52MHz.

The RXCLK16O and RXCLK16_32O output drivers are designed to drive a 50Ω transmission line. The

transmission line can be DC terminated with a split-end termination scheme (see Figure 3), or DC terminated by

50Ω to VCC-2V on each line (see Figure 4). AC-coupling can be achieved by a number of methods. Figure 5

illustrates an AC-coupling method for the occasion when the downstream device provides the bias point for

AC-coupling. The divide-by-16 output (RXCLK16O) or the divide-by-16 or -32 output (RXCLK16_32O) can

be used to provide an external looptiming reference clock (after external filtering with a 1x REFCLK PLL) for

the clock multiplication unit on the VSC8140.

The RXOUT[15:0] output drivers are designed to drive a 50Ω transmission line which can be DC termi-

nated with a split-end termination scheme (see Figure 6), or a traditional termination scheme (see Figure 7).

Figure 6: Split-end DC Termination of Low-Speed LVPECL RXOUT[15:0] Outputs

VSC8140

Split-end equivalent termination is ZO to VTERM

R1 = 125Ω R2 = 83Ω, ZO=50Ω, VTERM= VCC-2V

Zo

VCC

R1 = 125Ω

R1||R2 = Zo

VCCR2 + VEER1

R1+R2

= VTERM

R2 = 83Ω

VEE

Page 4

© VITESSE SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

G52251-0, Rev. 4.0

9/6/00