X24C16 查看數據表(PDF) - Xicor -> Intersil

零件编号

产品描述 (功能)

生产厂家

X24C16 Datasheet PDF : 15 Pages

| |||

X24C16

Stop Condition

All communications must be terminated by a stop con-

dition, which is a LOW to HIGH transition of SDA when

SCL is HIGH. The stop condition is also used by the

X24C16 to place the device into the standby power

mode after a read sequence. A stop condition can only

be issued after the transmitting device has released the

bus.

Acknowledge

Acknowledge is a software convention used to indicate

successful data transfer. The transmitting device, either

master or slave, will release the bus after transmitting

eight bits. During the ninth clock cycle the receiver will

pull the SDA line LOW to acknowledge that it received

the eight bits of data. Refer to Figure 3.

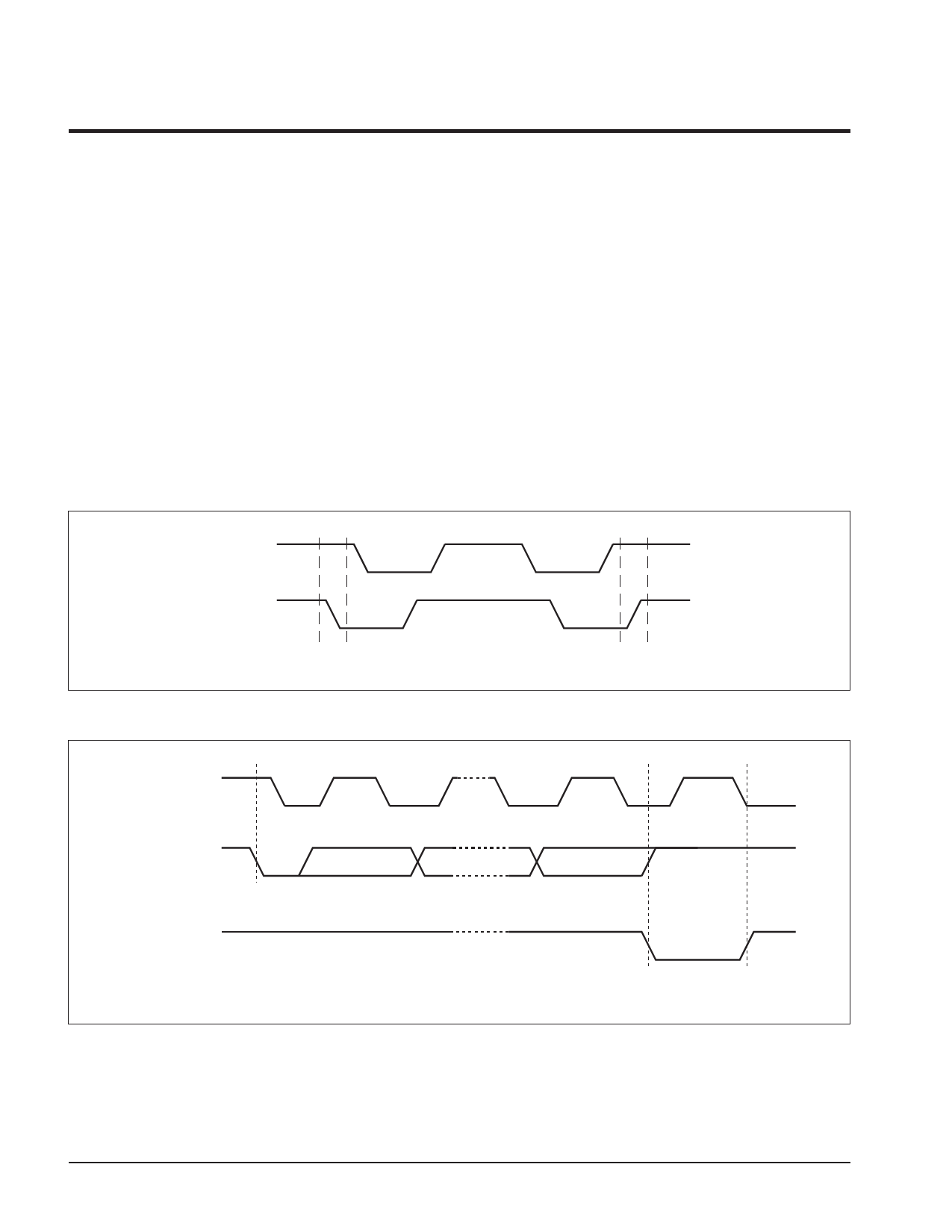

Figure 2. Definition of Start and Stop

The X24C16 will respond with an acknowledge after

recognition of a start condition and its slave address. If

both the device and a write operation have been se-

lected, the X24C16 will respond with an acknowledge

after the receipt of each subsequent eight bit word.

In the read mode the X24C16 will transmit eight bits of

data, release the SDA line and monitor the line for an

acknowledge. If an acknowledge is detected and no

stop condition is generated by the master, the X24C16

will continue to transmit data. If an acknowledge is not

detected, the X24C16 will terminate further data trans-

missions. The master must then issue a stop condition

to return the X24C16 to the standby power mode and

place the device into a known state.

SCL

SDA

START BIT

Figure 3. Acknowledge Response From Receiver

SCL FROM

MASTER

1

DATA

OUTPUT

FROM

TRANSMITTER

DATA

OUTPUT

FROM

RECEIVER

START

STOP BIT

3840 FHD F07

8

9

ACKNOWLEDGE

3840 FHD F08

4