E-L6452 查看數據表(PDF) - STMicroelectronics

零件编号

产品描述 (功能)

生产厂家

E-L6452 Datasheet PDF : 22 Pages

| |||

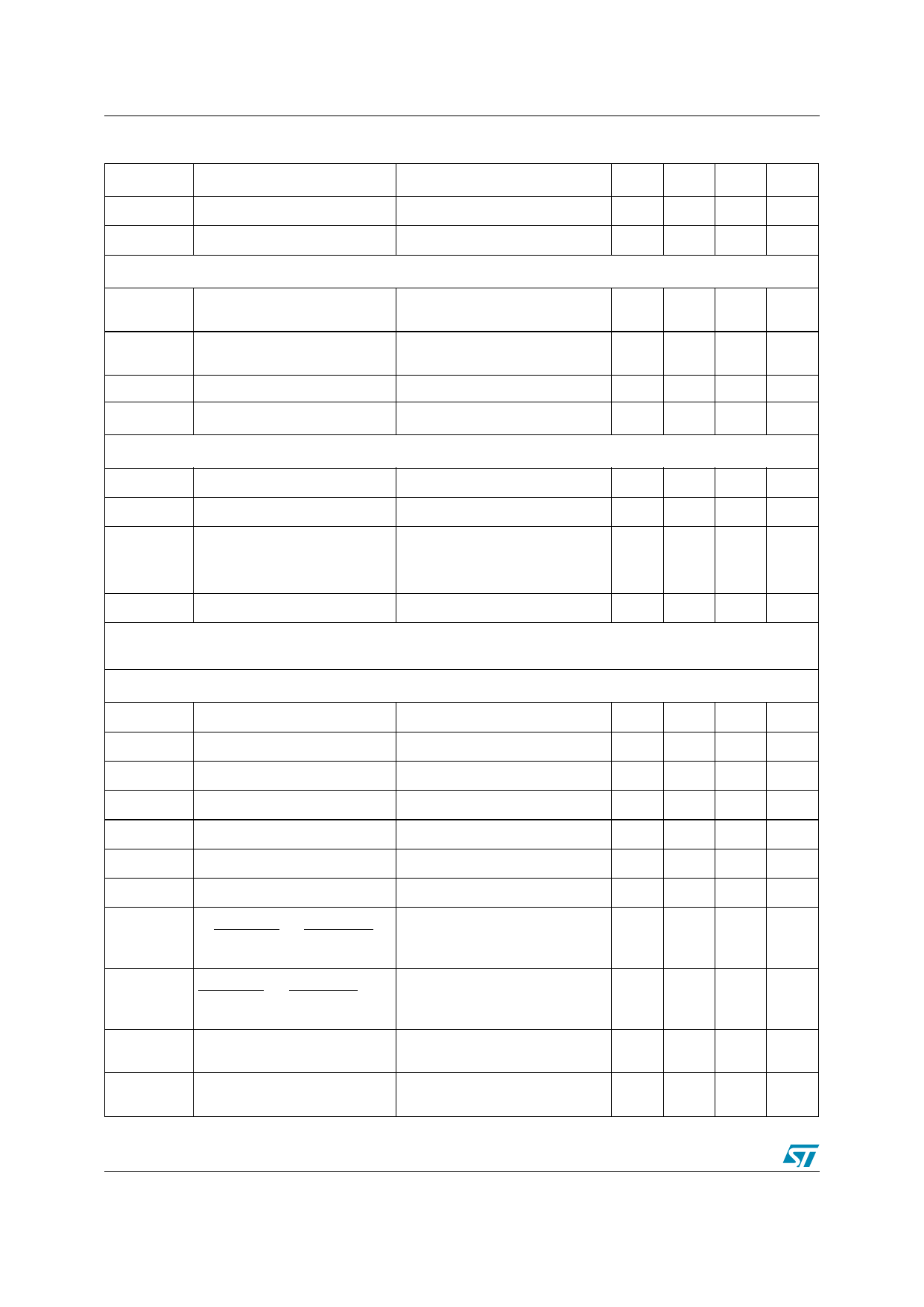

Electrical specifications

L6452

Table 3. DC Electrical characteristics (Tj = 25°C) - continued

Symbol

Parameter

Test Condition

Min. Typ. Max. Unit

Tacqth

Theoretical acquisition time

fadck= 250 kHz

32.4

µs

Tacqpr Real acquisition time

fadck= 250 kHz

36

µs

DIGITAL INTERFACE INPUT

Vinp

Vinm

Vhys

Iin

Schmitt Trigger positive-going

Threshold

Schmitt Trigger negative-going

Threshold

Schmitt Trigger Hysteresis

Input Current (Vin=0; Vdd=5) (4)

2/3Vdd V

1/3Vdd

V

0.1 0.3

1

V

50 150 300 µA

CR LATCH TIMINGS

Tls

Latch set up time

100

ns

Tlhigh

Latch high time

100

ns

Selected channel:

Tlconv

Latch data valid to A/D input

valid delay

CH1..CH5

4

µs

CH0

7

µs

tstore

Latching data time

200

ns

Note: The control register (driving signals CRdata, CRclock) is accessed with the same timing

specifications as the data 16 bit shift register (signals SDI, SDC)

SHIFT REGISTER AND LATCH TIMING

Ta

Tb

Tc

Td

Te

Tf

Tg

Tset

Thold

Tlp

Tpl

Set up time

Hold time

Serial clock low time

Serial clock high time

Serial clock period

Latch set up time

Latch data high time

NcEn setup time with respect

to LongPulse (or ShortPulse)

Asserted

NcEn hold time with respect to

LongPulse (or ShortPulse)

Asserted

Set-up time from latch to Pulse

(short and long)

Time from Pulse deassertion to

new data latching

35

ns

35

ns

35

ns

35

ns

125

ns

100

ns

100

ns

160

ns

0

ns

125

ns

125

ns

10/22