HYS64V2100GCU-10 查看數據表(PDF) - Siemens AG

零件编号

产品描述 (功能)

生产厂家

HYS64V2100GCU-10 Datasheet PDF : 12 Pages

| |||

HYS64(72)V2100G(C)U-10

2M x 64/72 SDRAM-Module

A serial presence detect storage device - E 2PROM - is assembled onto the module. Information

about the module configuration, speed, etc. is written into the E 2PROM device during module

production using a serial presence detect protocol ( I 2C synchronous 2-wire bus)

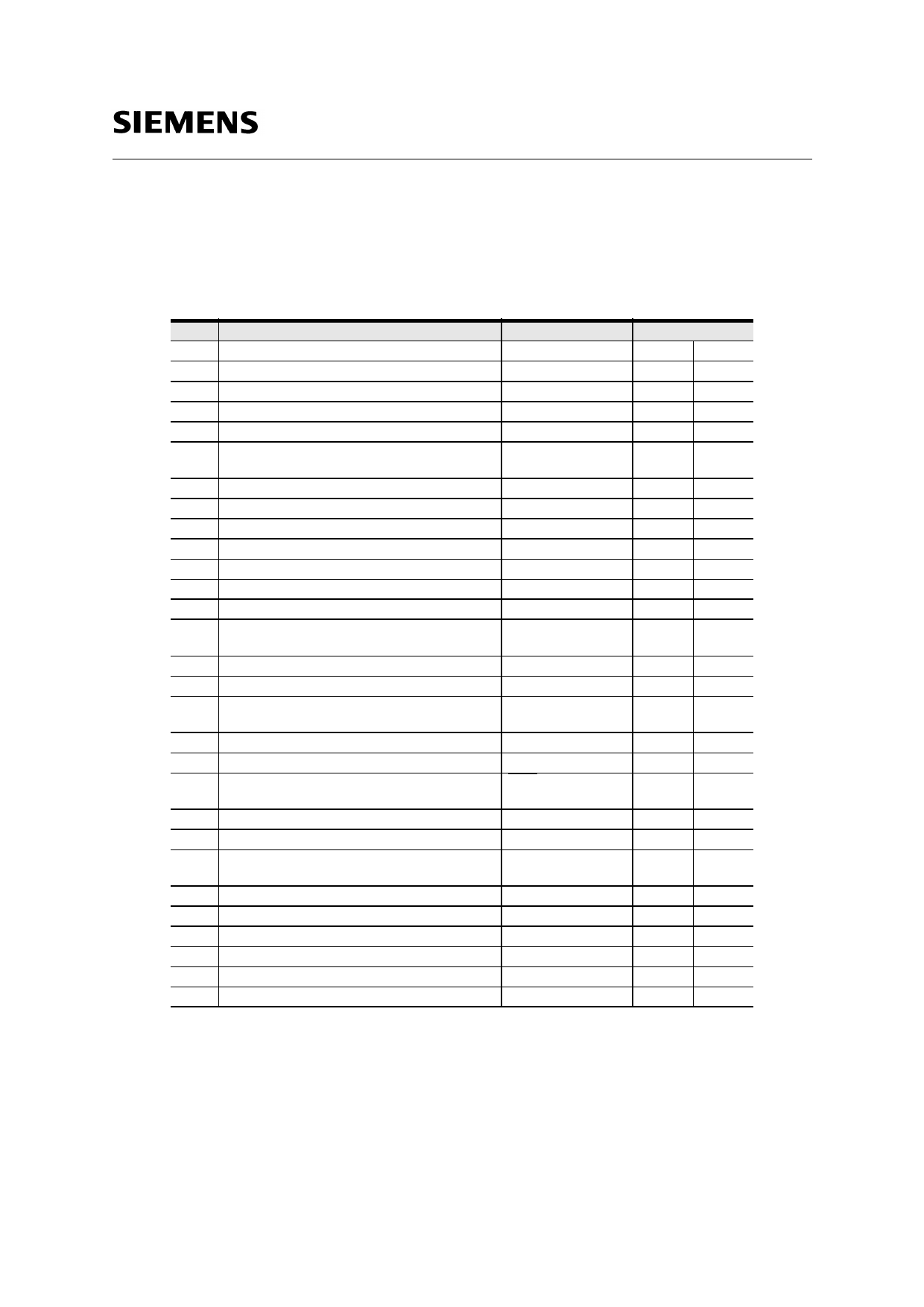

SPD-Table:

Byte#

Description

SPD Entry Value

0 Number of SPD bytes

128

1 Total bytes in Serial PD

256

2 Memory Type

SDRAM

3 Number of Row Addresses (without BS bits)

11

4 Number of Column Addresses (for x 8

9

SDRAM)

5 Number of DIMM Banks

1

6 Module Data Width

64 / 72

7 Module Data Width (contd’ )

0

8 Module Interface Levels

LVTTL

9 SDRAM Cycle Time at CL=3

8.0 / 10.0 / 12.0 ns

10 SDRAM Access time from Clock at CL=3

8.0 ns

11 Dimm Config (Error Det/Corr.)

none / ECC

12 Refresh Rate/Type

Self-Refresh,

15.6µs

13 SDRAM width, Primary

x8

14 Error Checking SDRAM data width

n/a / x8

15 Minimum clock delay for back-to-back ran-

dom column address

tccd = 1 CLK

16 Burst Length supported

1, 2, 4, 8 & full page

17 Number of SDRAM banks

2

18 Supported CAS Latencies

CAS latency = 1, 2

&3

19 CS Latencies

CS latency = 0

20 WE Latencies

Write latency = 0

21 SDRAM DIMM module attributes

non buffered/non

reg.

22 SDRAM Device Attributes :General

Vcc tol +/- 10%

23 SDRAM Cycle Time at CL = 2

15.0 ns

24 SDRAM Access time from Clock at CL = 2

9.0 ns

25 SDRAM Cycle Time at CL = 1

30 ns

26 SDRAM Access time from Clock at CL=1

27 ns

27 Minimum Row Precharge Time

30 ns

Hex

x64

x72

80

80

08

08

04

04

0B

0B

09

09

01

01

40

48

00

00

01

01

A0

A0

80

80

00

02

80

80

08

08

00

08

01

01

8F

8F

02

02

07

07

01

01

01

01

00

00

06

06

F0

F0

90

90

78

78

6C

6C

1E

1E

Semiconductor Group

10