PEEL22CV10AZ 查看數據表(PDF) - Anachip Corporation

零件编号

产品描述 (功能)

生产厂家

PEEL22CV10AZ Datasheet PDF : 10 Pages

| |||

Function Description

The implements logic functions as sum-of-products expressions in

a programmable-AND/fixed-OR logic array. User-defined

functions are created by programming the connections of input

signals into the array. User-configurable output structures in the

form of I/O macrocells further increase logic flexibility.

Architecture Overview

The architecture is illustrated in the block diagram of Figure 19.

Twelve dedicated inputs and 10 I/Os provide up to 22 inputs and

10 outputs for creating logic functions (see Figure 21). At the

core of the device is a programmable electrically-erasable AND

array that drives a fixed OR array. With this structure, the

PEEL™22CV10AZ can implement up to 10 sum-of-products

logic expressions.

Associated with each of the ten OR functions is an I/O macrocell

that can be independently programmed to one of four different

configurations in standard 22V10 mode, or any one of 12 config-

urations using the special “Plus” mode. The programmable mac-

rocells allow each I/O to be used to create sequential or

combinatorial logic functions of active-high or active-low polar-

ity, while providing three different feedback paths into the AND

array.

AND/OR Logic Array

The programmable AND array of the PEEL™22CV10AZ

(shown in Figure 21) is formed by input lines intersecting prod- uct

terms. The input lines and product terms are used as follows:

44 Input Lines:

– 24 input lines carry the true and complement of the signals

applied to the 12 input pins

– 20 additional lines carry the true and complement values of

feedback or input signals from the 10 I/Os

133 Product Terms:

– 120 product terms (arranged in 2 groups of 8, 10, 12, 14, and

16) are used to form sum of product functions

– 10 output enable terms (one for each I/O)

– 1 global synchronous preset term

– 1 global asynchronous clear term

– 1 programmable clock term

At each input-line/product-term intersection, there is an

EEPROM memory cell that determines whether or not there is a

logical connection at that intersection. Each product term is

essentially a 44-input AND gate. A product term that is con-

nected to both the true and complement of an input signal will

always be FALSE and therefore will not affect the OR function

that it drives. When all the connections on a product term are

opened, a “don’t care” state exists and that term will always be

TRUE.

grammer first performs a bulk erase to remove the previous pat-

tern. The erase cycle opens every logical connection in the array.

The device is configured to perform the user-defined function by

programming selected connections in the AND array. (Note that

PEEL™ device programmers automatically program all of the

connections on unused product terms so that they will have no

effect on the output function).

Variable Product Term Distribution

The PEEL™22CV10AZ provides 120 product terms to drive the

10 OR functions. These product terms are distributed among the

outputs in groups of 8, 10, 12, 14, and 16 to form logical sums

(see Figure 21). This distribution allows optimum use of the

device resources.

Programmable I/O Macrocell

The unique twelve-configuration output macrocell provides com-

plete control over the architecture of each output. The ability to

configure each output independently lets you to tailor the config-

uration of the PEEL™22CV10AZ to the precise requirements of

your design.

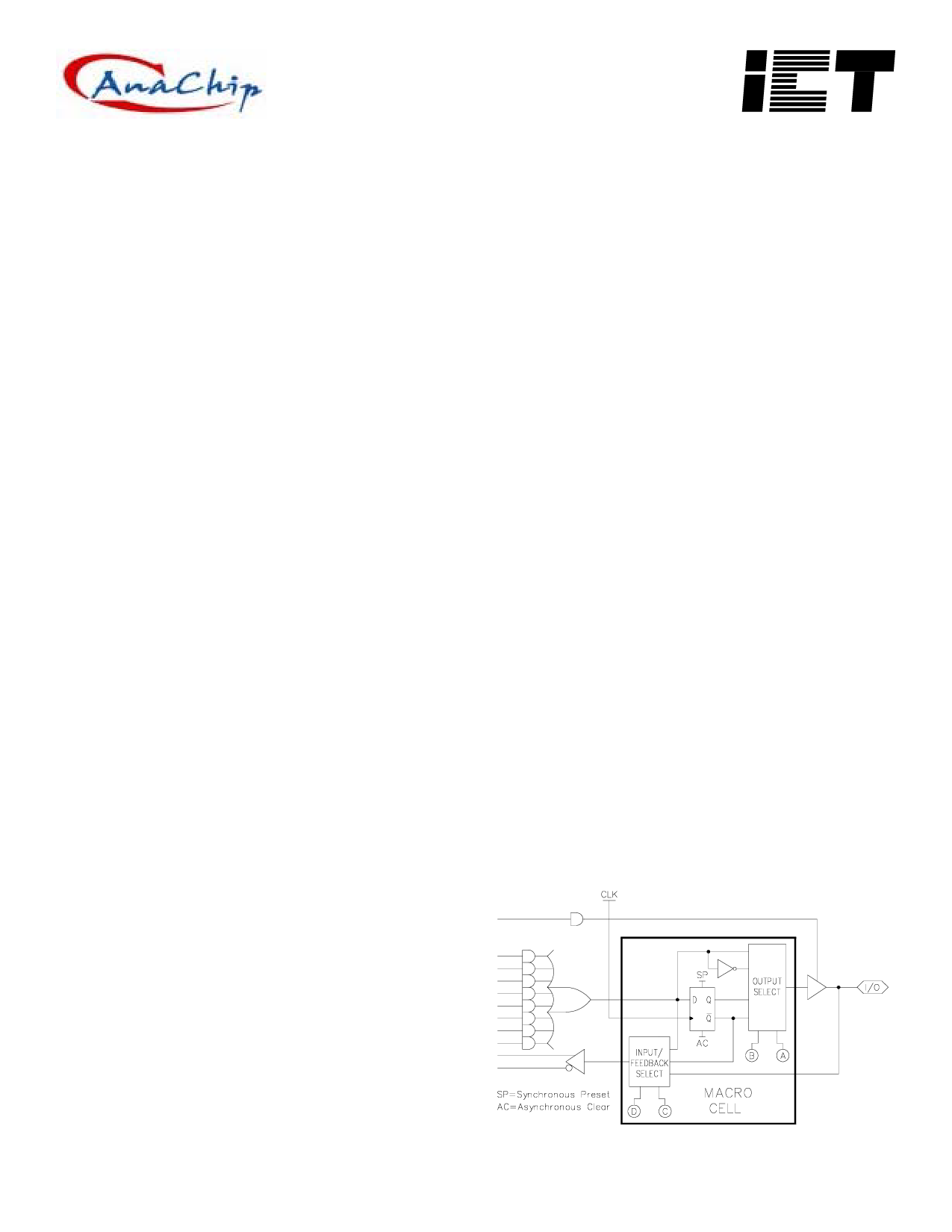

Macrocell Architecture

Each I/O macrocell, as shown in Figure 20, consists of a D-type

flip-flop and two signal-select multiplexers. The configuration of

the macrocell is determined by four EEPROM bits that control the

multiplexers. These bits determine the output polarity, output type

(registered or non-registered) and input-feedback path (bidi-

rectional I/O, combinatorial feedback). Refer to Table 1. for

details. Four of these macrocells duplicate the functionality of the

industry-standard PAL22V10. (See Figure 21 and Table 1.)

Figure 20 Block Diagram of the

PEEL™22CV10A I/O Macrocell

When programming the PEEL™22CV10AZ, the device pro-

Anachip Corp.

www.anachip.com.tw

3/10

Rev. 1.0 Dec 16, 2004