HD74CDCV857 查看數據表(PDF) - Renesas Electronics

零件编号

产品描述 (功能)

生产厂家

HD74CDCV857 Datasheet PDF : 13 Pages

| |||

HD74CDCV857

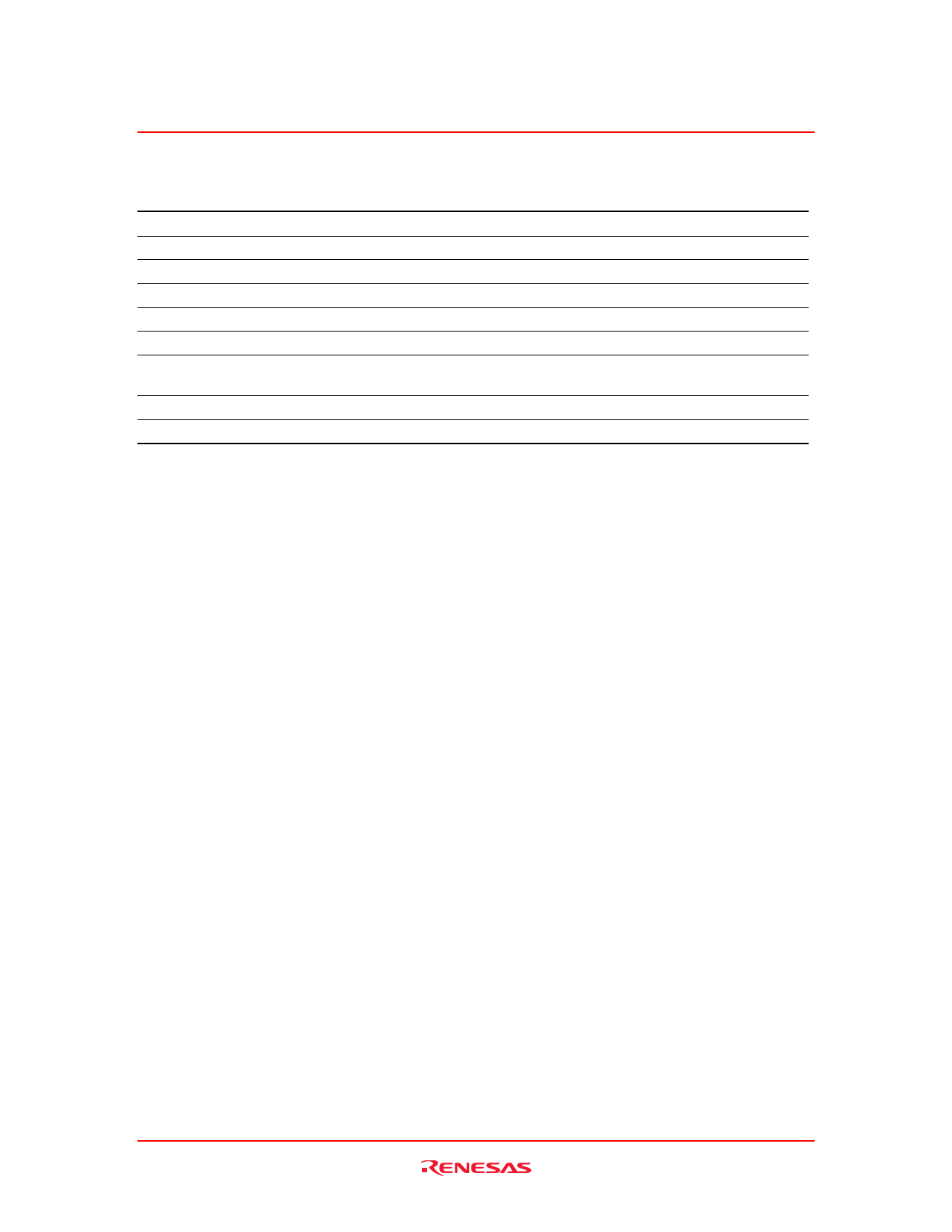

Switching Characteristics

Item

Symbol Min

Typ

Max

Unit Test Conditions Notes

Period jitter

tPER

–75

—

75

ps See figure 6, 9 7, 8

Half period jitter

tHPER

–100

—

100

ps See figure 7, 9 8, 10

Cycle to cycle jitter

tCC

–75

—

75

ps See figure 5, 9 10

Static phase offset

tSPE

–75

—

75

ps See figure 3, 9 4, 5, 9, 10

Output clock skew

tsk

—

—

100

ps See figure 4, 9

Operating clock frequency fCLK(O) 60

—

200

MHz See figure 9

1, 2

Application clock

frequency

fCLK(A)

95

133

170

MHz See figure 9

1, 3

Slew rate

tSL

1.0

—

2.0

V/ns See figure 9

20% – 80%

PLL stabilization time

tSTAB

—

—

0.1

ms See figure 9

6, 10

Notes: 1. The PLL must be able to handle spread spectrum induced skew (the specification for this

frequency modulation can be found in the latest Intel PC100 Registered DIMM specification)

2. Operating clock frequency indicates a range over which the PLL must be able to lock, but in

which it is not required to meet the other timing parameters.

3. Application clock frequency indicates a range over which the PLL must meet all timing

parameters.

4 Assumes equal wire length and loading on the clock output and feedback path.

5. Static phase offset does not include jitter.

6. Stabilization time is the time required for the integrated PLL circuit to obtain phase lock of its

feedback signal to its reference signal after power up.

7. Period jitter defines the largest variation in clock period, around anominal clock period.

8. Period jitter and half period jitter are independent from each other.

9. Conditions at VDDQ = 2.5 V, Ta = 25°C.

10. Guaranteed by design, not 100% tested in production.

Rev.7.00, Oct.09.2003, page 8 of 12