LC99062-W50 查看數據表(PDF) - SANYO -> Panasonic

零件编号

产品描述 (功能)

生产厂家

LC99062-W50 Datasheet PDF : 7 Pages

| |||

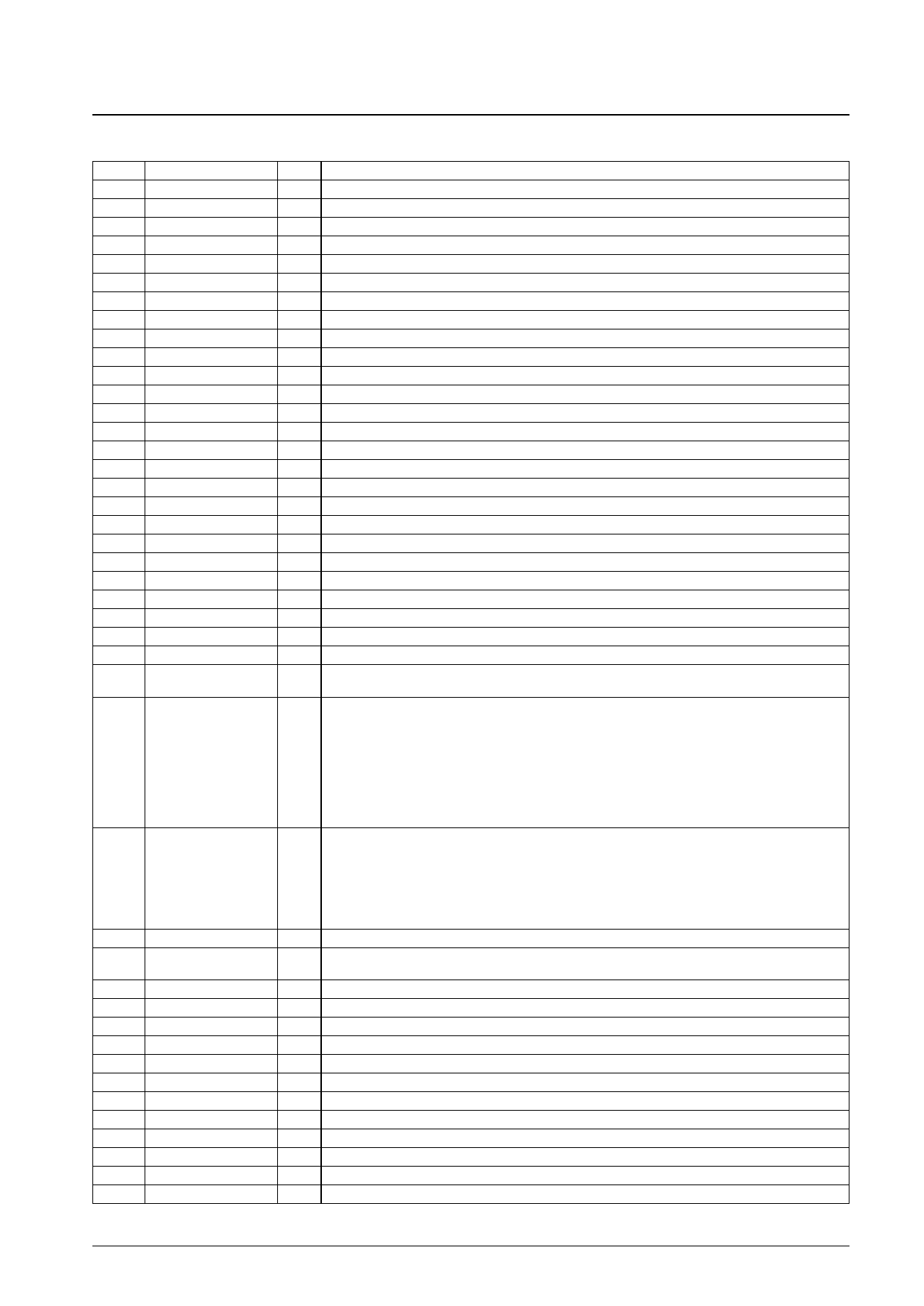

Continued from preceding page.

Pin No.

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

Symbol

BIN8

BIN7

BIN6

BIN5

BIN4

BIN3

BIN2

BIN1

VDD

GIN8

GIN7

GIN6

GIN5

GIN4

GIN3

GIN2

GIN1

VSS

RIN8

RIN7

RIN6

RIN5

RIN4

RIN3

RIN2

RIN1

CSSET2

82

OMODE0

83

OMODE1

84

OMODE2

85

IMODE0

86

IMODE1

87

WBMD1

88

WBHLH

89

VDD

90

VSS

91

WBMD2

92

WBMD3

93

REG1

94

REG2

95

REG3

96

REG4

97

REG5

98

REG6

99

REG7

100

REG8

LC99062-W50

I/O → I: Input pin, O: Output pin, B: Bidirectional pin, P: Power supply pin, NC: Unconnected pin

I/O

Function

I 8-bit data input (MSB)

I 8-bit data input

I 8-bit data input

I 8-bit data input

I 8-bit data input

I 8-bit data input or register setting pin

I 8-bit data input or register setting pin

I 8-bit data input (LSB) or register setting pin

P

I 8-bit data input (MSB)

I 8-bit data input

I 8-bit data input

I 8-bit data input

I 8-bit data input

I 8-bit data input or register setting pin

I 8-bit data input or register setting pin

I 8-bit data input (LSB) or register setting pin

P

I 8-bit data input (MSB)

I 8-bit data input

I 8-bit data input

I 8-bit data input

I 8-bit data input

I 8-bit data input or register setting pin

I 8-bit data input or register setting pin

I 8-bit data input (LSB) or register setting pin

Must be set according to the phase of the LC99052 A/D converter clock. (This is true for pin 52 as well.)

I

Recommended value for current conditions: 1

Output mode select

000: Video (OT1 to OT8), ICON (OT24)

001: R (OT1 to OT8), G (OT9 to OT16), B (OT17 to OT24)

I 010: R-Y (OT1 to OT8), Y (OT9 to OT16), B-Y (OT17 to OT24)

I 011: Y (OT1 to OT8), C (OT9 to OT16), CSYNC (OT24)

I 100: Y (OT1 to OT8), U/V (OT9 to OT16), UVCONT (OT24)

101: VBS (OT1 to OT8), Y (OT12 to OT9), R-Y (OT16, OT15), B-Y (OT14, OT13)

110: VBS (OT1 to OT8), Y + CSYNC (OT9 to OT16), C (OT17 to OT24)

111: Y/U/V (OT1 to OT8)

Input mode select

00: R (RIN4 to RIN8), G (GIN4 to GIN8), B (BIN4 to BIN8)*1

01: R (RIN4 to RIN8), G (GIN4 to GIN8), B (BIN4 to BIN8)*2

I

10: R (RIN1 to RIN8), G (GIN1 to GIN8), B (BIN1 to BIN8)*1

I

11: Y (RIN1 to RIN8), V (GIN1 to GIN8), U (BIN1 to BIN8)*1

Note: 1. The output is synchronized with the chrominance key out.

2. The chrominance key out is output 16 clock cycles in advance of this output.

I White balance mode SW1

Auto white balance hold; 1: Hold, 0: Auto

I

Note: * Hold this pin low when the internal register is used.

P

P

I White balance mode SW2

I White balance mode SW3

I Register setting pin

I Register setting pin

I Register setting pin

I Register setting pin

I Register setting pin

I Register setting pin

I Register setting pin

I Register setting pin

No. 5073-4/7