NTE3882 查看數據表(PDF) - NTE Electronics

零件编号

产品描述 (功能)

生产厂家

NTE3882 Datasheet PDF : 4 Pages

| |||

AC Characteristics (Cont’d): (TA = 0° to 70°C, VCC = 5V ±5% unless otherwise specified)

Parameter

Symbol Test Conditions Min Typ Max Unit

Clock ↓ to Data Out Delay

TdC(DO) Note 3

––

240

ns

Clock ↑ to Data Out Float Delay

TdC(DOz)

––

230

ns

Data In to Clock ↑ Setup Time

TsDI(C)

60 –

ns

M1 to Clock ↑ Setup Time (INTA or M1 Cycle)

TsM1(C)

210 –

–

ns

M1 ↓ to IEO ↓ Delay (Interrupt Immediately

Preceding M1)

TdM1(IEO) Note 4, Note 5

––

300

ns

IORQ ↓ to Data Out Delay (INTA Cycle)

TdIO(DOT) Note 3

––

340

ns

IEI ↓ to IEO ↓ Delay

TdIEI(IEOf) Note 4

––

190

ns

IEI ↑ to IEO ↑ Delay (After ED Decode)

TdIEI(IEOr) Note 4

––

220

ns

Clock ↑ to INT ↓ Delay

TdC(INT) Timer Mode

– – TcT + 220 ns

CLR/TRG ↑ to INT ↓ (TsCTR(C) Satisfied)

TdCTK(INT) Counter Mode

– – TcC + 230 ns

CLR/TRG ↑ to INT ↓ (TsCTR(C) Not Satisfied)

– – 2TcC + 530 ns

CLK Cycle Time

TcCTR Counter Mode 2TcC –

–

ns

CLK/TRG Rise Time

TrCTR

––

50

ns

CLK/TRG Fall Time

TfCTR

––

50

ns

CLK/TRG Width (Low)

TwCTRL

200 –

–

ns

CLK/TRG Width (High)

TwCTRH

200 –

–

ns

CLK ↑ to Clock ↑ Setup Time for Immediate Count TsCTR(Cc) Counter Mode 300 –

–

ns

TRG ↑ to Clock ↑ Setup Time for Enabling of

Prescaler on Following Clock ↑

TsCTR(Ct) Timer Mode

210 –

–

ns

Clock ↑ to ZC/TO ↑ Delay

TdC(ZCTOr)

260 –

–

ns

Clock ↓ to ZC/TO ↓ Delay

190 –

–

ns

Note 3. Increase delay by 10ns for each 50pF increase in loading, 200pF maximum for data lines

and 100pF for control lines.

Note 4. Increase delay by 10ns for each 10pF increase in loading, 100pF maximum.

Note 5. 2.5 TcC > (N–2) TdIEI(IEOF) + TdIM1(IEO) + TsIEI(IO).

Note 6. RESET must be active for a minimum of 3 clock cycles.

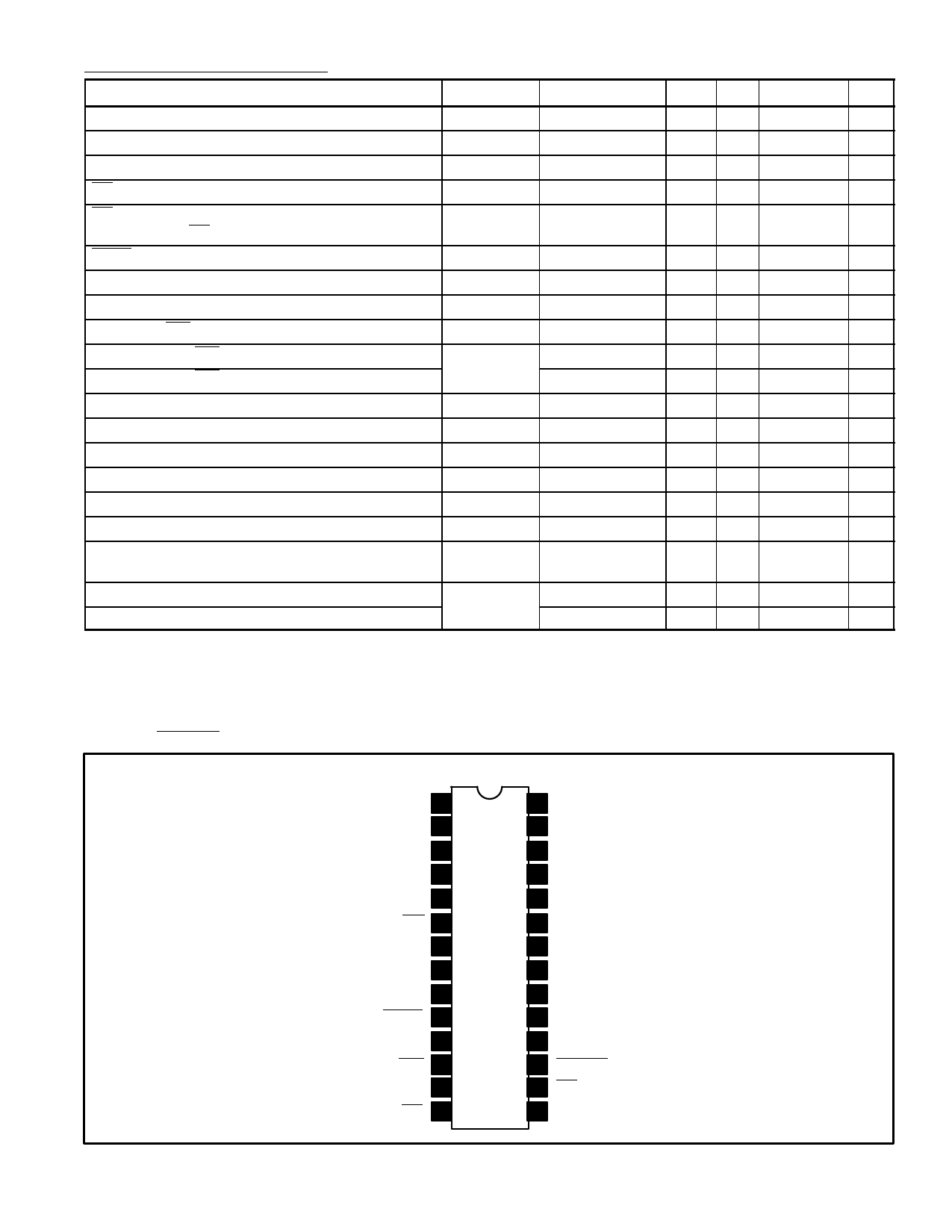

Pin Connection Diagram

D4 1

D5 2

D6 3

D7 4

GND 5

RD 6

ZC/TO0 7

ZC/TO1 8

ZC/TO2 9

IORQ 10

IEO 11

INT 12

IEI 13

M1 14

28 D3

27 D2

26 D1

25 D0

24 (+) 5V

23 CLK/TRG0

22 CLK/TRG1

21 CLK/TRG2

20 CLK/TRG3

19 CS1

18 CS0

17 RESET

16 CE

15 System Clock Input