NT256D72S89AKGU 查看數據表(PDF) - Unspecified

零件编号

产品描述 (功能)

生产厂家

NT256D72S89AKGU Datasheet PDF : 15 Pages

| |||

NT256D72S89AKGU

256MB : 32M x 72

Low Profile Registered DDR SDRAM DIMM

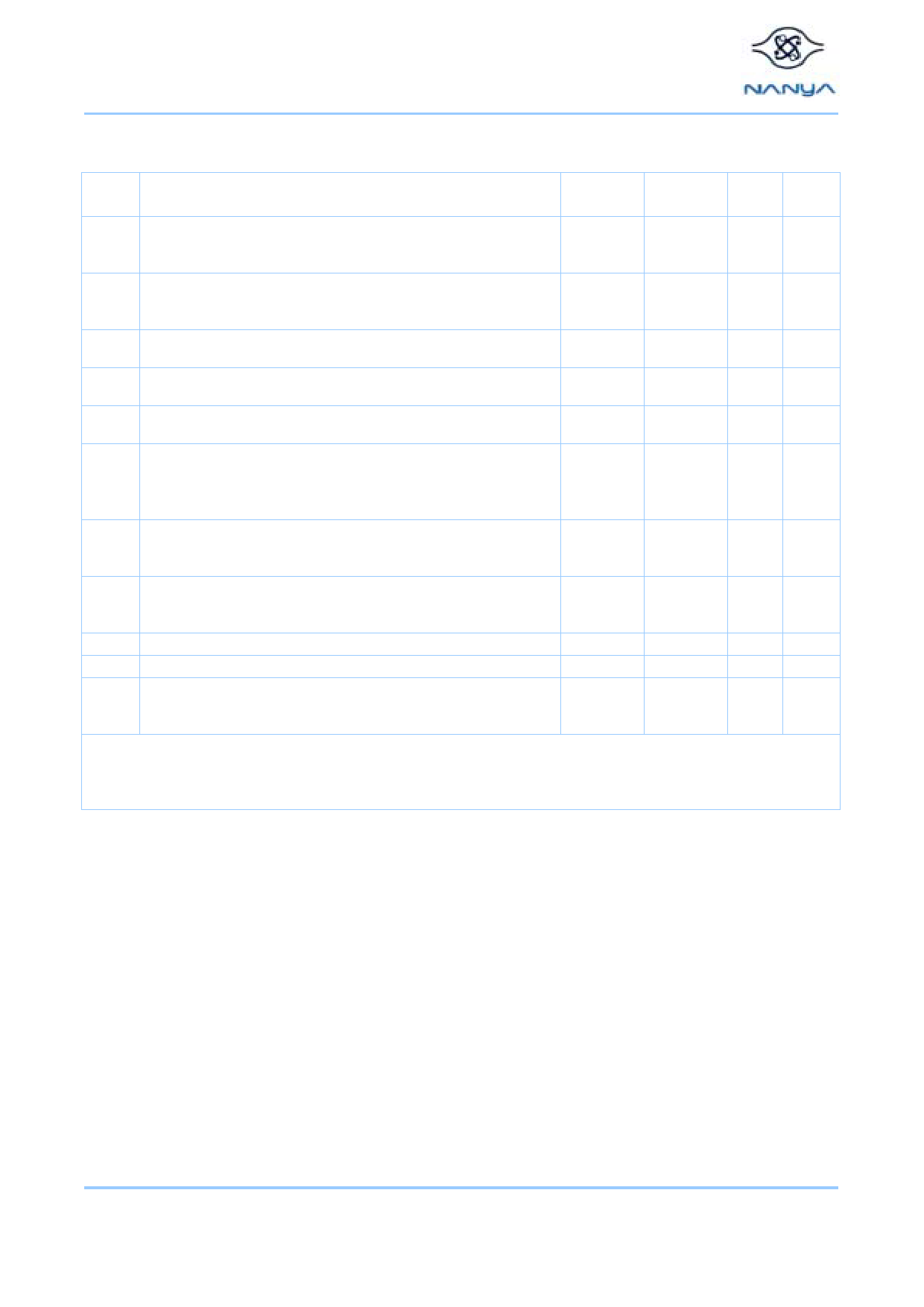

Operating, Standby, and Refresh Currents

(TA = 0 °C ~ 70 °C; VDDQ = 2.5V ± 0.2V; VDD = 2.5V ± 0.2V, See AC Characteristics)

Symbol

Parameter/Condition

I DD0

Operating Current: one bank; active/precharge; tRC = tRC (MIN); tCK = tCK

(MIN); DQ, DM, and DQS inputs changing twice per clock cycle; address and

control inputs changing once per clock cycle

I DD1

Operating Current: one bank; active/read/precharge; Burst = 2; tRC = tRC

(MIN); CL=2.5; tCK = tCK (MIN); IOUT = 0mA; address and control inputs

changing once per clock cycle

I DD2P

I DD2N

Precharge Power-Down Standby Current: all banks idle; power-down

mode; CKE ≤ VIL (MAX); tCK = tCK (MIN)

Idle Standby Current: CS ≥ VIH (MIN); all banks idle; CKE ≥ VIH (MIN); tCK =

tCK (MIN); address and control inputs changing once per clock cycle

I DD3P

I DD3N

Active Power-Down Standby Current: one bank active; power-down mode;

CKE ≤ VIL (MAX); tCK = tCK (MIN)

Active Standby Current: one bank; active/precharge; CS ≥ VIH (MIN); CKE ≥

VIH (MIN); tRC = tRAS (MAX); tCK = tCK (MIN); DQ, DM, and DQS inputs

changing twice per clock cycle; address and control inputs changing once

per clock cycle

I DD4R

Operating Current: one bank; Burst = 2; reads; continuous burst; address

and control inputs changing once per clock cycle; DQ and DQS outputs

changing twice per clock cycle; CL = 2.5; tCK = tCK (MIN); IOUT = 0mA

I DD4W

Operating Current: one bank; Burst = 2; writes; continuous burst; address

and control inputs changing once per clock cycle; DQ and DQS inputs

changing twice per clock cycle; CL=2.5; tCK = tCK (MIN)

I DD5 Auto-Refresh Current: tRC = tRFC (MIN)

I DD6 Self-Refresh Current: CKE ≤ 0.2V

Operating Current: four bank; four bank interleaving with BL = 4, address

I DD7 and control inputs randomly changing; 50% of data changing at every

transfer; tRC = tRC (min); IOUT = 0mA.

1. I DD specifications are tested after the device is properly initialized.

2. Input slew rate = 1V/ ns.

3. Enables on-chip refresh and address counters.

4. Current at 7.8 µs is time averaged value of IDD5 at tRFC (MIN) and IDD2P over 7.8 µs.

PC2100

(-7K/-75B)

TBD

TBD

TBD

TBD

TBD

TBD

TBD

TBD

TBD

TBD

TBD

PC1600

(-8K)

TBD

TBD

TBD

TBD

TBD

TBD

TBD

TBD

TBD

TBD

TBD

Unit Notes

mA

1, 2

mA

1, 2

mA

1, 2

mA

1, 2

mA

1, 2

mA

1, 2

mA

1, 2

mA

1, 2

mA 1, 2, 4

mA

1, 2

mA

1, 2

REV 0.2 (Preliminary)

09/2002

10

© NANYA TECHNOLOGY CORP.

NANYA TECHNOLOGY CORP. reserves the right to change Products and Specifications without notice.