DS1775R-U 查看數據表(PDF) - Maxim Integrated

零件编号

产品描述 (功能)

生产厂家

DS1775R-U Datasheet PDF : 15 Pages

| |||

DS1775

Digital Thermometer and Thermostat in SOT23

AC Electrical Characteristics-2 Wire Interface

(VDD = 2.7V to 5.5V, TA = -55°C to +125°C, unless otherwise noted.) (Figure 5)

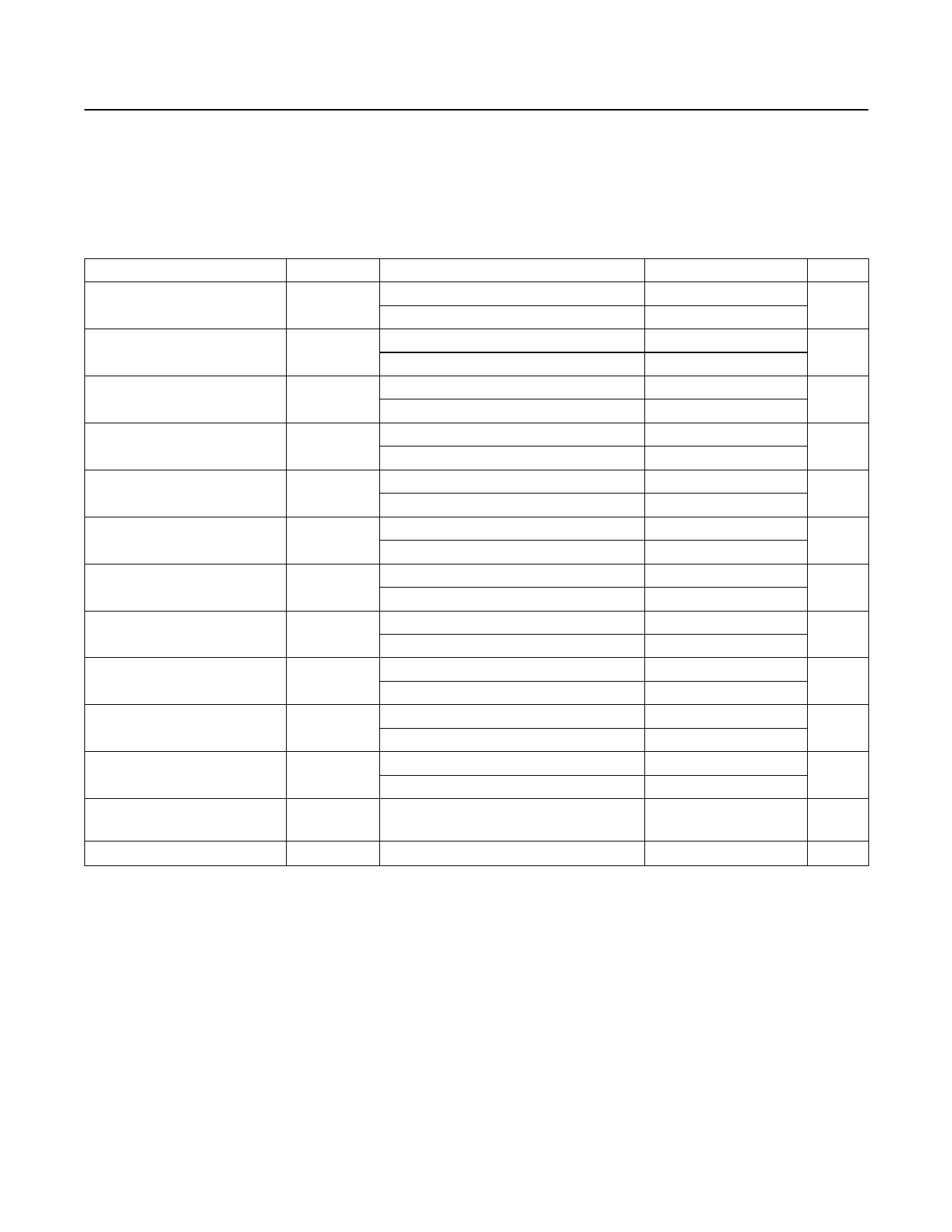

PARAMETER

SCL Clock Frequency

Bus Free Time Between a

STOP and START Condition

Hold Time (Repeated) START

Condition

Low Period of SCL

High Period of SCL

Setup Time for a

Repeated START

Data Hold Time

Data Setup Time

Rise Time of Both SDA and

SCL Signals

Fall Time of Both SDA and SCL

Signals

Setup Time for STOP

Capacitive Load for Each Bus

Line

SYMBOL

fSCL

tBUF

tHD:STA

tLOW

tHIGH

tSU:STA

tHD:DAT

tSU:DAT

tR

tF

tSU:STO

CB

CONDITIONS

Fast mode

Standard mode

Fast mode

Standard mode

Fast mode (Note 5)

Standard mode (Note 5)

Fast mode

Standard mode

Fast mode

Standard mode

Fast mode

Standard mode

Fast mode (Note 6)

Standard mode (Note 6)

Fast mode (Note 7)

Standard mode (Note 7)

Fast mode (Note 8)

Standard mode (Note 8)

Fast mode (Note 8)

Standard mode (Note 8)

Fast mode

Standard mode

(Note 8)

MIN TYP

1.3

4.7

0.6

4.0

1.3

4.7

0.6

4.0

0.6

4.7

0

0

100

250

20 + 0.1CB

20 + 0.1CB

20 + 0.1CB

20 + 0.1CB

0.6

4.0

MAX

400

100

UNITS

kHz

µs

µs

µs

µs

µs

0.9

µs

0.9

ns

300

ns

1000

300

ns

300

µs

400

pF

Input Capacitance

CI

5

pF

Note 1: All voltages are referenced to ground.

Note 2:

Note 3:

Note 4:

Note 5:

I/O pins of fast mode devices must not obstruct the SDA and SCL lines if VDD is switched off.

IDD specified with O.S. pin open.

IDD specified with VDD at 5.0V and VSDA, VSCL = 5.0V, 0°C to +70°C.

After this period, the first clock pulse is generated.

Note 6: The maximum tHD:DAT has only to be met if the device does not stretch the low period (tLOW) of the SCL signal.

Note 7: A fast mode device can be used in a standard mode system, but the requirement tSU:DAT ≥ 250ns must then be met. This is

automatically the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low

period of the SCL signal, it must output the next data bit to the SDA line tR MAX + tSU:DAT = 1000 + 250 = 1250ns before the

SCL line is released.

Note 8: CB = Total capacitance of one bus line in pF.

Note 9: Internal heating caused by O.S. loading causes the DS1775 to read approximately 0.5°C higher if O.S. is sinking the max

rated current.

Note 10: Contact the factory for operation requiring temperature readings greater than +120°C.

www.maximintegrated.com

Maxim Integrated │ 3