MAX6467(2002) 查看數據表(PDF) - Maxim Integrated

零件编号

产品描述 (功能)

生产厂家

MAX6467

(Rev.:2002)

(Rev.:2002)

MAX6467 Datasheet PDF : 9 Pages

| |||

Microprocessor Supervisory Reset Circuits

with Edge-Triggered, One-Shot Manual Reset

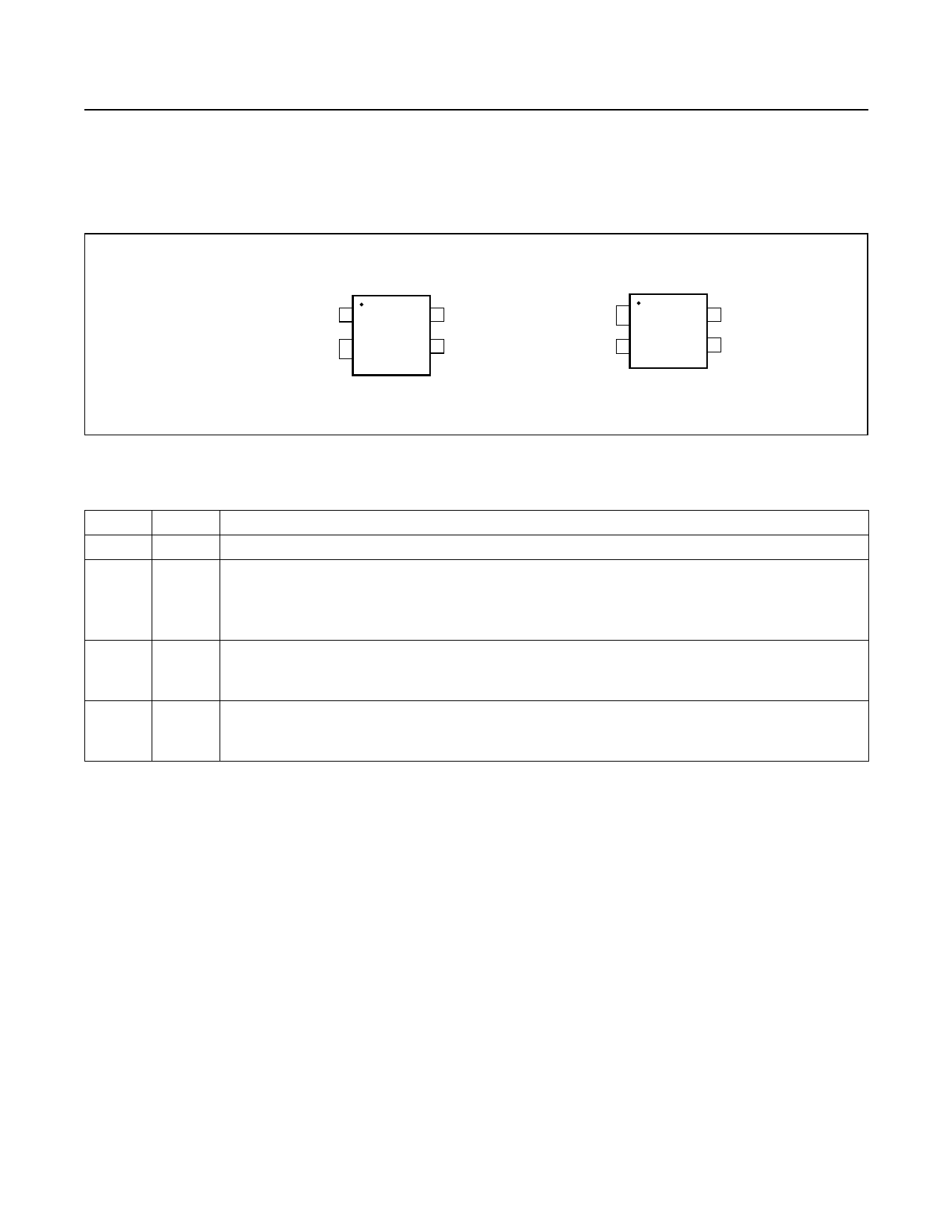

Pin Description

PIN

NAME

FUNCTION

1

GND Ground

Reset Output. RESET is an active-low open-drain (MAX6467) or push-pull (MAX6468) output. RESET asserts

2

RESET

low when VCC drops below the selected threshold and remains low for the VCC reset timeout period after

VCC rises above the threshold. The RESET one-shot asserts low for a fixed MR reset timeout period on the

falling edge of the manual reset input. The open-drain output requires an external pullup resistor.

Manual Reset Input. Drive MR low to initiate a reset output. MR controls an edge-triggered one-shot that

3

MR asserts RESET low for a fixed MR timeout period when MR is driven low. Internal timing circuitry ignores

switch close and open bounce to ensure proper one-shot reset timing.

Power-Supply Input. VCC provides power to the device and is also a monitored voltage. When VCC drops

4

VCC below the selected threshold, RESET asserts low and remains low for the reset timeout period after VCC rises

above the threshold. For better noise immunity, bypass VCC to GND with a 0.1µF capacitor.

VCC

VTH

GND

SWITCH

SWITCH

SWITCH

BOUNCE

BOUNCE

BOUNCE

MR

GND

RESET

tRP

tMRP

tDEB

tMRP

GND

Figure 1. Timing Diagram

Detailed Description

Reset Output

The MAX6467 provides an active-low open-drain

RESET output. The MAX6468 provides an active-low

push-pull RESET output. RESET asserts low if VCC

drops below the selected threshold or if a falling edge

occurs on MR. RESET remains low for the VCC reset

timeout period after VCC increases above the threshold

voltage or is one-shot pulsed low for the MR timeout

period after a falling edge on MR.

Manual Reset Input

Many µP-based products require manual reset capability,

allowing the operator, a test technician, or external logic

circuitry to initiate a reset. A falling edge on MR asserts

RESET low. RESET is one-shot pulsed low for the MR

timeout period after a falling edge on MR. An internal

1.5kΩ pullup resistor to VCC allows MR to be left uncon-

nected if not used. MR can be driven with TTL or CMOS-

logic levels, or with open-drain/collector outputs. Connect

a normally open momentary pushbutton switch from MR

to GND to realize a manual reset function. External

debounce circuitry is not required, as the MAX6467/

MAX6468 respond to the first falling edge on MR and

ignore subsequent falling edges within the reset timeout

period and during the MR debounce period (see Figure

1). After MR goes high for 150ms (tDEB), the manual reset

one-shot is ready to trigger a reset on the next MR falling

edge. Connect a 0.1µF capacitor from MR to GND when

using long cables to provide additional noise immunity

(Figure 2).

_______________________________________________________________________________________ 5