ADUM1400 查看數據表(PDF) - Analog Devices

零件编号

产品描述 (功能)

生产厂家

ADUM1400 Datasheet PDF : 31 Pages

| |||

ADuM1400/ADuM1401/ADuM1402

Data Sheet

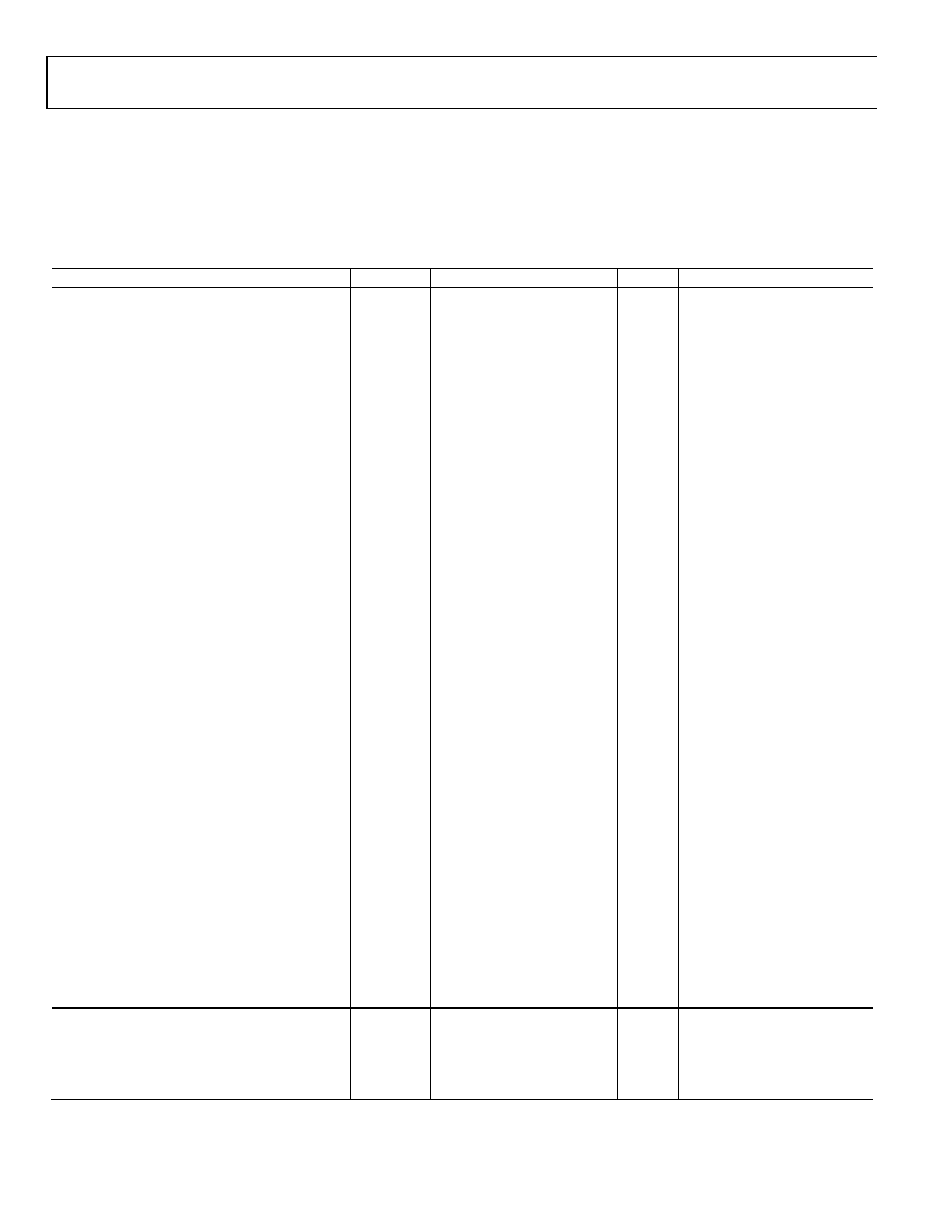

SPECIFICATIONS

ELECTRICAL CHARACTERISTICS—5 V, 105°C OPERATION1

4.5 V ≤ VDD1 ≤ 5.5 V, 4.5 V ≤ VDD2 ≤ 5.5 V; all minimum/maximum specifications apply over the entire recommended operation range,

unless otherwise noted; all typical specifications are at TA = 25°C, VDD1 = VDD2 = 5 V. These specifications do not apply to ADuM1400W,

ADuM1401W, and ADuM1402W automotive grade versions.

Table 1.

Parameter

DC SPECIFICATIONS

Input Supply Current per Channel, Quiescent

Output Supply Current per Channel, Quiescent

ADuM1400 Total Supply Current, Four Channels2

DC to 2 Mbps

VDD1 Supply Current

VDD2 Supply Current

10 Mbps (BRW and CRW Grades Only)

VDD1 Supply Current

VDD2 Supply Current

90 Mbps (CRW Grade Only)

VDD1 Supply Current

VDD2 Supply Current

ADuM1401 Total Supply Current, Four Channels2

DC to 2 Mbps

VDD1 Supply Current

VDD2 Supply Current

10 Mbps (BRW and CRW Grades Only)

VDD1 Supply Current

VDD2 Supply Current

90 Mbps (CRW Grade Only)

VDD1 Supply Current

VDD2 Supply Current

ADuM1402 Total Supply Current, Four Channels2

DC to 2 Mbps

VDD1 or VDD2 Supply Current

10 Mbps (BRW and CRW Grades Only)

VDD1 or VDD2 Supply Current

90 Mbps (CRW Grade Only)

VDD1 or VDD2 Supply Current

For All Models

Input Currents

Logic High Input Threshold

Logic Low Input Threshold

Logic High Output Voltages

Logic Low Output Voltages

SWITCHING SPECIFICATIONS

ADuM1400ARW/ADuM1401ARW/ADuM1402ARW

Minimum Pulse Width3

Maximum Data Rate4

Propagation Delay5

Symbol

IDDI (Q)

IDDO (Q)

IDD1 (Q)

IDD2 (Q)

IDD1 (10)

IDD2 (10)

IDD1 (90)

IDD2 (90)

IDD1 (Q)

IDD2 (Q)

IDD1 (10)

IDD2 (10)

IDD1 (90)

IDD2 (90)

IDD1 (Q), IDD2 (Q)

I , I DD1 (10) DD2 (10)

I , I DD1 (90) DD2 (90)

IIA, IIB, IIC,

IID, IE1, IE2

VIH, VEH

VIL, VEL

VOAH, VOBH,

VOCH, VODH

VOAL, VOBL,

VOCL, VODL

PW

tPHL, tPLH

Min

−10

2.0

(VDD1 or VDD2) − 0.1

(VDD1 or VDD2) − 0.4

1

50

Typ

0.50

0.19

2.2

0.9

8.6

2.6

70

18

1.8

1.2

7.1

4.1

57

31

1.5

5.6

44

+0.01

5.0

4.8

0.0

0.04

0.2

65

Max

0.53

0.21

2.8

1.4

10.6

3.5

100

25

2.4

1.8

9.0

5.0

82

43

2.1

7.0

62

+10

0.8

0.1

0.1

0.4

1000

100

Unit

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

µA

V

V

V

V

V

V

V

ns

Mbps

ns

Test Conditions

DC to 1 MHz logic signal freq.

DC to 1 MHz logic signal freq.

5 MHz logic signal freq.

5 MHz logic signal freq.

45 MHz logic signal freq.

45 MHz logic signal freq.

DC to 1 MHz logic signal freq.

DC to 1 MHz logic signal freq.

5 MHz logic signal freq.

5 MHz logic signal freq.

45 MHz logic signal freq.

45 MHz logic signal freq.

DC to 1 MHz logic signal freq.

5 MHz logic signal freq.

45 MHz logic signal freq.

0 V ≤ VIA, VIB, VIC, VID ≤ VDD1 or VDD2,

0 V ≤ VE1, VE2 ≤ VDD1 or VDD2

IOx = −20 µA, VIx = VIxH

IOx = −3.2 mA, VIx = VIxH

IOx = 20 µA, VIx = VIxL

IOx = 400 µA, VIx = VIxL

IOx = 3.2 mA, VIx = VIxL

CL = 15 pF, CMOS signal levels

CL = 15 pF, CMOS signal levels

CL = 15 pF, CMOS signal levels

Rev. L | Page 4 of 31