ENW89815CXKF 查看數據表(PDF) - Panasonic Corporation

零件编号

产品描述 (功能)

生产厂家

ENW89815CXKF Datasheet PDF : 34 Pages

| |||

CLASSIFICATION

Einstufung

SUBJECT

Thema

CUSTOMER’S CODE

PAN1455/1555

PRODUCT SPECIFICATION

Produktspezifikation

CLASS 2 BLUETOOTH MODULE

Bluetooth Modul der Klasse 2

PANASONIC’S CODE

ENW89815CxKF/ENW89815AxKF

No.

REV.

DS-1x55-2400-102

1.10

PAGE

Seite

10 of 34

DATE

Datum

27.06.2011

7. TERMINAL SPECIFICS

Interfacebeschreibungen

7.1.

RF-INTERFACE - ANT

The PAN1455 presents a 50Ω impedance on the antenna pin. If you need antenna support

please e-mail to wireless@ecom.panasonic.de or use the PAN1555 with integrated ceramic

antenna.

7.2.

POWER SUPPLY

PAN1455/1555 require a power supply with the following characteristics:

Typical : 3.3VDC, min.: 3.0VDC – max.: 3.6VDC, low noise (≤10mV), >80mA peak

Due to the technological requirements and the pulsed radio transmission the supply needs to

be fed by an ultra fast (response time ≤20µs) linear regulator placed as close as possible to

the VSUP pin (16). Functionality has been verified with the following types: TOREX:

XC6204x332xx or XC6401xx42xx

It is also recommended to place a low ESR capacitor with at least 10µF as close as possible

to the VSUP pin (16).

NOTE: You must ensure that during operation the supply voltage never drops below 2.8 VDC.

Otherwise the flash contents (firmware and/or configuration data) can get lost.

7.3.

POWER-ON-RESET

PAN1455/1555 are equipped with circuitry for generating Power ON/-OFF Reset from the

internal core voltage. A reset is generated when the core voltage falls below typically 1.88V

and is released when it rises above typically 1.92V.

In case of Power-On, Power-Off, Watchdog, Low-Power or Software, RESET# acts as an

Output by holding RESET# at ≤ 0.3V for min. 1,5ms and max. 3,5ms.

In an application with an external Reset as an Input, for example external Reset-Controller,

we recommend to use Open-Drain-Output for this circuit. An external reset shall be generated

at RESET# ≤ 0.3V for ≥ 5ms after VSUP has stabilized in the recommended voltage range.

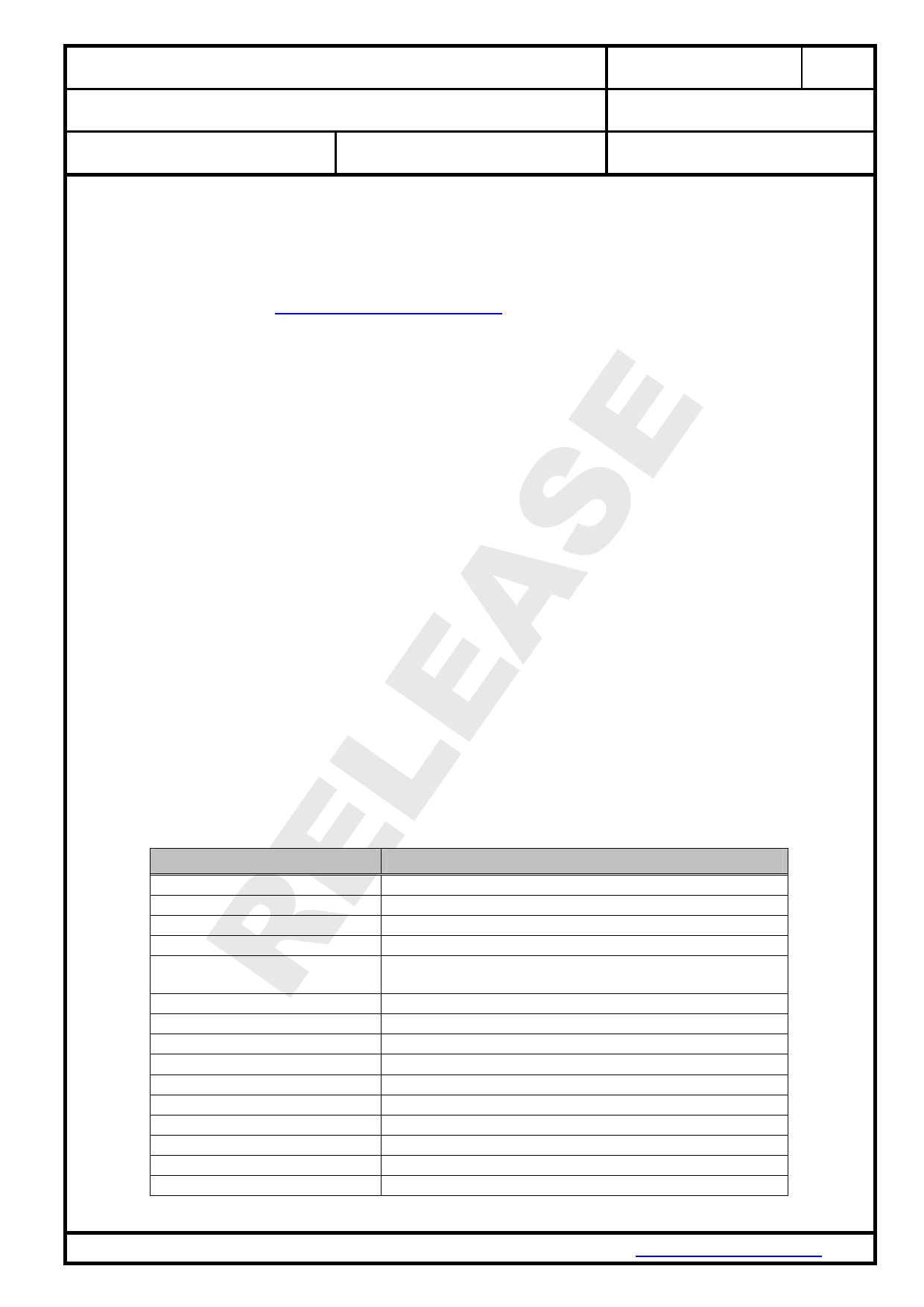

The following table shows the pin states of PAN1455/1555 on reset.

Pin Name

State: PAN1455/1555

UART_RTS#

UART_TXD

UART_RXD

UART_CTS#

GPIO[0] – GPIO[13], GPIO[16],

GPIO[17]

GPIO[14]

GPIO[15]

Boot0

ATRST

ATDI

ATMS

ATDO

ATCK

USB_DM

USB_DP

Input Floating

Input Floating

Input Floating

Input Pull-Up

Input Floating

Input Pull-Up

Input Pull-Up

Input Pull-Down

Input Pull-Up

Input Pull-Up

Input Pull-Up

Input Floating

Input Pull-Down

Input Floating

Input Floating

PANASONIC ELECTRONIC DEVICES EUROPE GMBH

www.pedeu.pansonic.de