EVAL-ADIS2 查看數據表(PDF) - Analog Devices

零件编号

产品描述 (功能)

生产厂家

EVAL-ADIS2 Datasheet PDF : 20 Pages

| |||

ADIS16362

Data Sheet

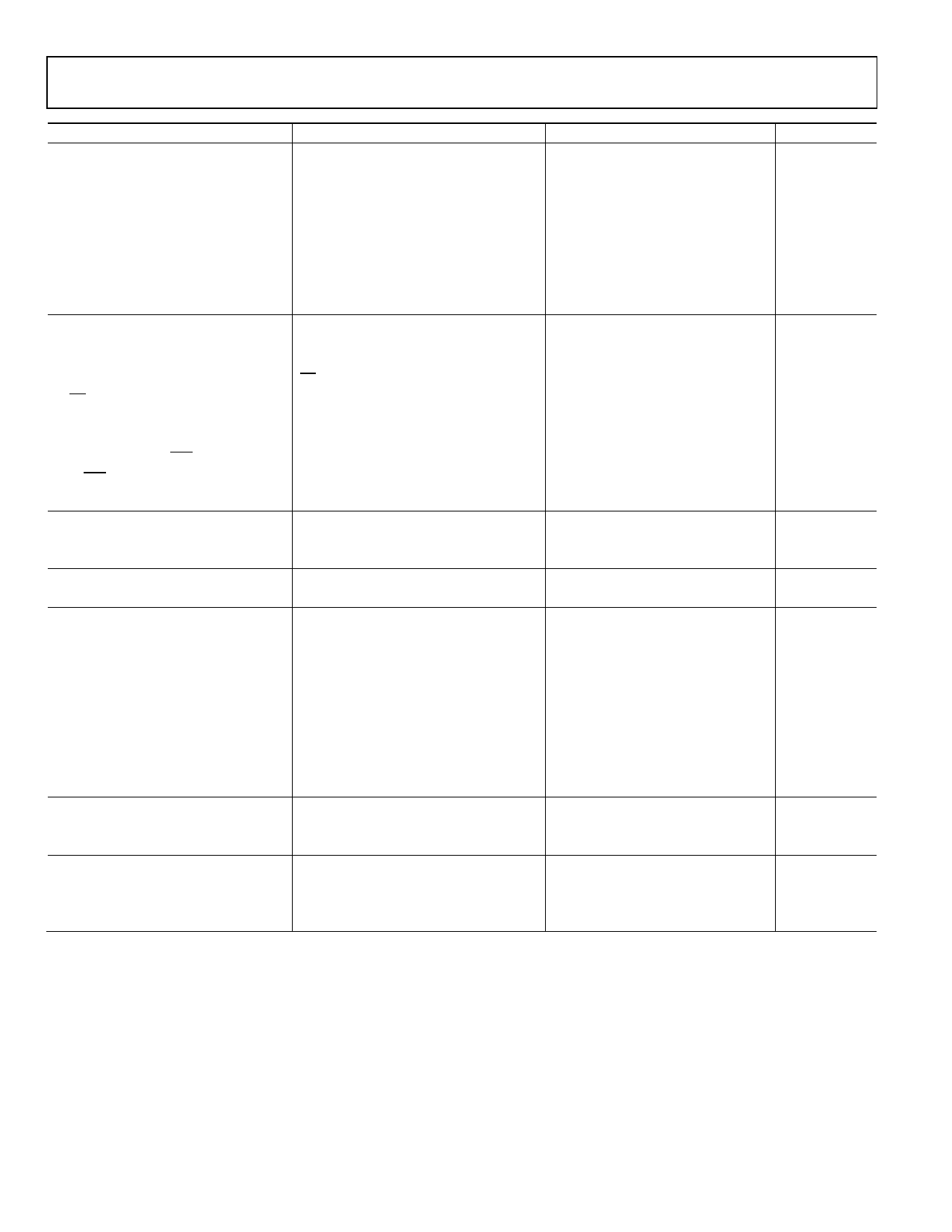

Parameter

DAC OUTPUT

Resolution

Relative Accuracy

Differential Nonlinearity

Offset Error

Gain Error

Output Range

Output Impedance

Output Settling Time

LOGIC INPUTS2

Input High Voltage, VIH

Input Low Voltage, VIL

CS Wake-Up Pulse Width

Logic 1 Input Current, IIH

Logic 0 Input Current, IIL

All Pins Except RST

RST Pin

Input Capacitance, CIN

DIGITAL OUTPUTS2

Output High Voltage, VOH

Output Low Voltage, VOL

FLASH MEMORY

Data Retention4

FUNCTIONAL TIMES5

Power-On Start-Up Time

Reset Recovery Time

Sleep Mode Recovery Time

Flash Memory Test Time

Automatic Self-Test Time

CONVERSION RATE

Clock Accuracy

Sync Input Clock

POWER SUPPLY

Power Supply Current

Test Conditions/Comments

5 kΩ/100 pF to GND

101 LSB ≤ input code ≤ 4095 LSB

Min

Typ

12

±4

±1

±5

±0.5

0

2

10

2.0

CS signal to wake up from sleep mode

20

VIH = 3.3 V

±0.2

VIL = 0 V

40

1

10

ISOURCE = 1.6 mA

2.4

ISINK = 1.6 mA

Endurance3

10,000

TJ = 85°C

20

Time until data is available

Normal mode, SMPL_PRD ≤ 0x09

180

Low power mode, SMPL_PRD ≥ 0x0A

250

Normal mode, SMPL_PRD ≤ 0x09

60

Low power mode, SMPL_PRD ≥ 0x0A

130

Normal mode, SMPL_PRD ≤ 0x09

4

Low power mode, SMPL_PRD ≥ 0x0A

9

Normal mode, SMPL_PRD ≤ 0x09

17

Low power mode, SMPL_PRD ≥ 0x0A

90

SMPL_PRD = 0x01

12

SMPL_PRD = 0x01 to 0xFF

0.413

Operating voltage range, VCC

Low power mode

Normal mode

Sleep mode

0.86

4.75

5.0

24

49

500

Max

3.3

0.8

0.55

±10

60

0.4

819.2

±3

1.2

5.25

Unit

Bits

LSB

LSB

mV

%

V

Ω

µs

V

V

V

µs

µA

μA

mA

pF

V

V

Cycles

Years

ms

ms

ms

ms

ms

ms

ms

ms

ms

SPS

%

kHz

V

mA

mA

µA

1 X-ray exposure may degrade this performance metric.

2 The digital I/O signals are driven by an internal 3.3 V supply, and the inputs are 5 V tolerant.

3 Endurance is qualified as per JEDEC Standard 22, Method A117, and measured at −40°C, +25°C, +85°C, and +125°C.

3 The data retention lifetime equivalent is at a junction temperature (TJ) of 85°C as per JEDEC Standard 22, Method A117. Data retention lifetime decreases with junction

temperature.

5 These times do not include thermal settling and internal filter response times (330 Hz bandwidth), which may affect overall accuracy.

6 The sync input clock functions below the specified minimum value, at reduced performance levels.

Rev. F | Page 4 of 20